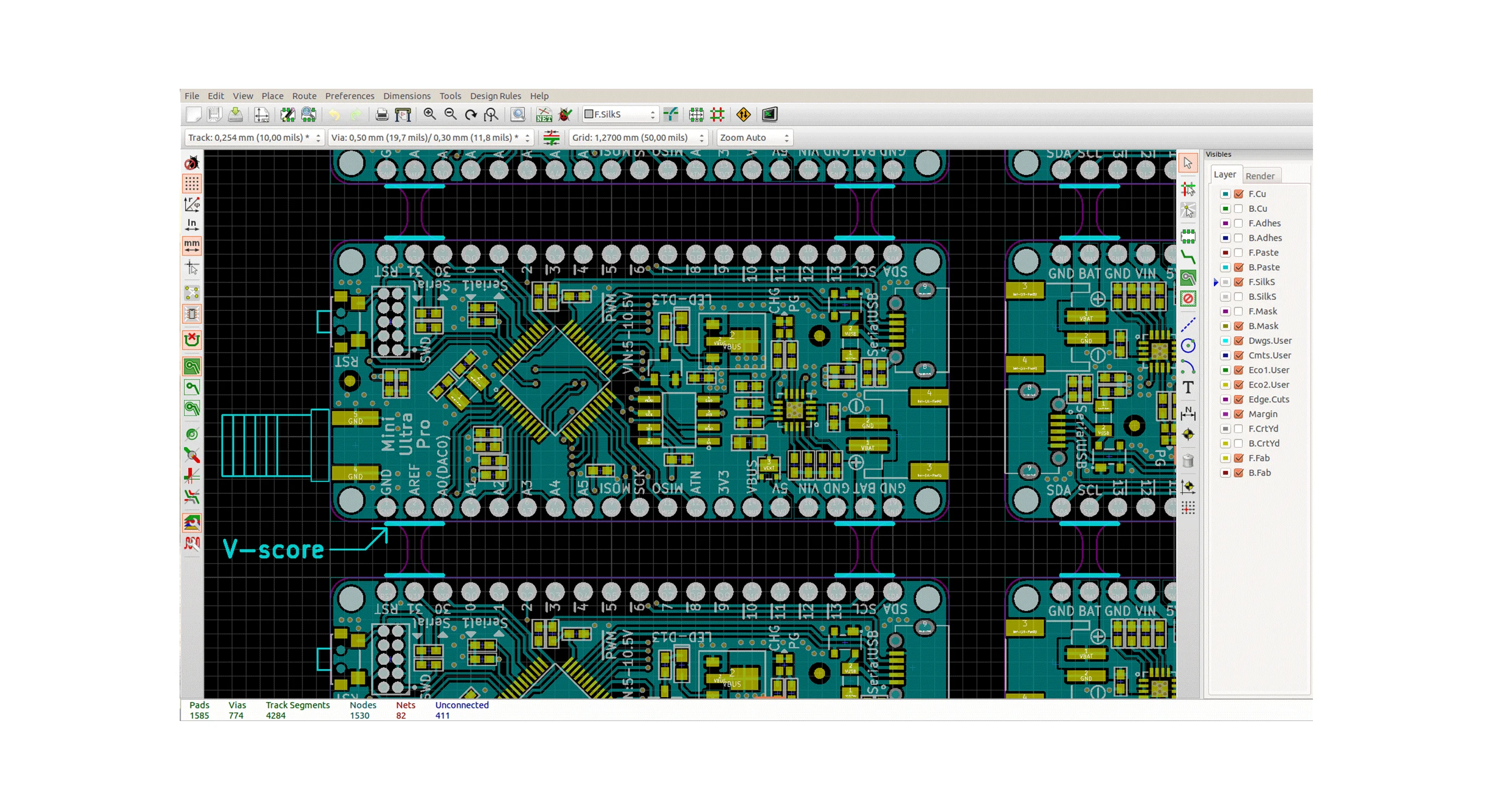

Mixed signal PCB design OC48 card layout and digital wiring

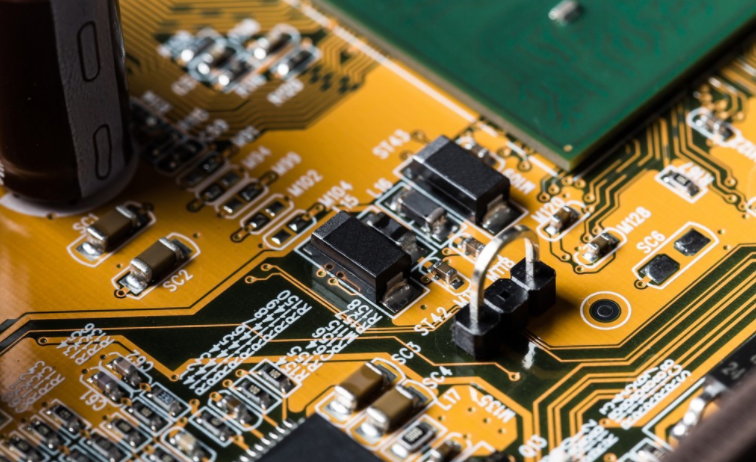

OC48 card layout

The high-speed analog signal between optICal transceiver and DSP is very sensitive to external noise SIMilarly, all special power supply and reference voltage circuits will cause a lot of coupling between analog and digital power transmission circuits of the card SometiMES, due to the shape of the chassis, high-density boards must be designed Because of the position of the external optical cable access card and the relatively high PCB assembly optical transceiver, the transceiver position in the card is basically fixed The system I/O connector position and signal distribution are also fixed This is the basic work that must be completed before layout

Like the most successful high-density analog layout and routing scheme, the layout must meet the routing requirements, and the layout and routing requirements must be balanced For the analog part of a mixed signal PCB and a local CPU core with 2V working voltage, the "layout before wiring" method is not recommended For OC48 card, DSP analog circuit (including analog reference voltage and analog power bypass capacitor) shall be connected interactively first After the wiring is completed, the entire DSP with analog components and wiring shall be close to the optical transceiver to fully ensure that the wiring length from the high-speed analog differential signal to the DSP is the shortest, with the least bending and through-hole Symmetry of differential placement and routing will reduce the impact of common mode noise However, it is difficult to predict the optimal layout before routing

Circuit board

Please consult the chip distributor for PCB layout design guidelines. Before designing according to the guidelines, it is necessary to fully communicate with the distributor's application engineers. Many chip distributors have strict time limits in providing high-quality layout suggestions. Sometimes, the solutions they provide are feasible for the "first class customers" who use the equipment. In the field of signal integrity design, the signal integrity design of new devices is particularly important. According to the basic guidelines of the distributor and the specific requirements of each power and ground pin in the package, you can start to lay out and wire the OC48 card with integrated DSP and microprocessor.

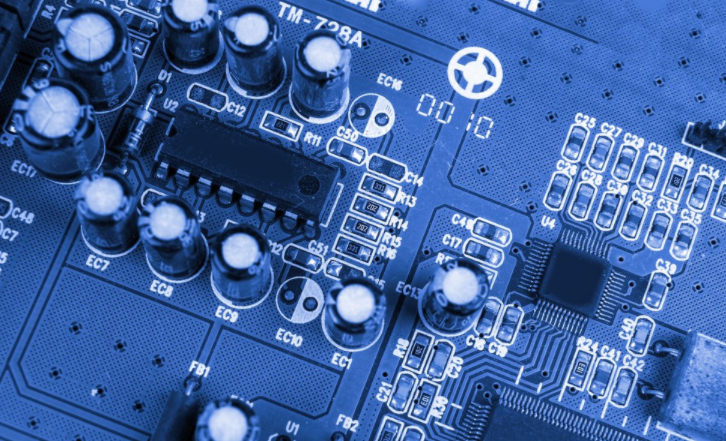

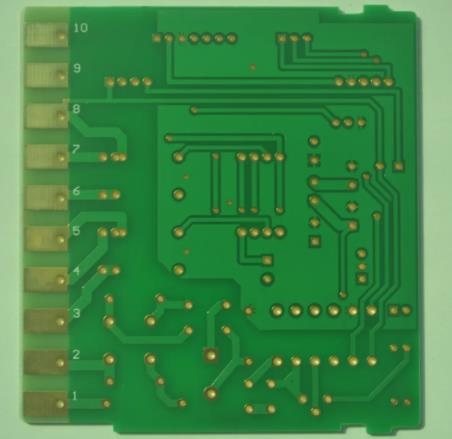

After determining the location and wiring of the high-frequency analog part, the remaining digital circuits can be placed according to the grouping method shown in the block diagram. The following circuits shall be carefully designed: the position of PLL power filter circuit in the CPU is highly sensitive to analog signals; Local CPU core voltage regulator; The reference voltage circuit of the "digital" microprocessor.

At this point, the power and manufacturing guidelines for digital wiring can be correctly applied to the design. The signal integrity design of the high-speed digital bus and clock signal above reveals some special wiring topology requirements for delay matching of processor bus, balanced Ts and some clock signal wiring. But you may not know that some people have also put forward an updated proposal, that is, to add some terminal resistors.

In the process of solving the problem, it is natural to make some adjustments in the layout phase. However, before starting the wiring, a very important step is to verify the timing of the digital part according to the layout. At this point, a complete DFM/DFT layout review of the board will help ensure that the card meets customer needs.

Digital wiring of OC48 card

For the power cord of the digital device and the digital part of the mixed signal DSP, the digital wiring should start from the SMD escape mode. Use the shortest and widest printing line allowed by the assembly process. For high-frequency equipment, the printed circuit of the power supply is equivalent to a SMAll inductance, which will worsen the power noise and lead to unnecessary coupling between analog circuits and digital circuits. The longer the power trajectory, the greater the inductance.

The best layout and wiring scheme can be obtained by using digital bypass capacitors. In short, fine tune the position of the bypass capacitor as required to make it easy to install and distribute it around the digital part and digital part of the mixed signal equipment. Route the bypass capacitor using the same "shortest and widest path" method.

When the power supply branch needs to pass through a continuous plane (such as the 3.3V power plane on the OC48 interface card), the power supply pin and the bypass capacitor do not have to share the same outlet diagram, and the lowest inductance and ESR bypass can be obtained. On the mixed signal PCB such as the OC48 interface card, pay special attention to the wiring of the power supply branch. Remember to place additional bypass capacitors on the entire card in a matrix arrangement, and place the power supply even near the passive components. After you determine the chart, you can start automatic routing. ATE test contact on OC48 card shall be defined during logIC design. Ensure that ATE contacts 100% of the nodes. In order to achieve ATE test with 0.070 inch minimum ATE test probe, the position of the opening and closing hole must be reserved to ensure that the power supply surface will not be interrupted by the cross cutting of the reverse pole of the through hole.

If a power and ground plane separation solution is to be used, layer offsets should be selected on adjacent wiring layers parallel to the opening. According to the perimeter of the opening area, the wiring prohibition area is defined on the adjacent layer to prevent wiring from entering. If the wiring must pass through the open area to another layer, make sure that the other layer adjacent to the wiring is a continuous ground plane. This reduces the reflection path. The layout of some digital signals is conducive to the use of bypass capacitors on the open power plane, but it is not recommended to bridge the digital and analog power planes, because noise will be coupLED to each other through bypass capacitors.

Some of the latest automatic routing applications can route high-density multilayer digital circuits. In the initial cabling phase, use 0.050 inch large size through-hole spacing at the SMD outlet, and consider the type of package used. The subsequent routing phase should allow vias to be close to each other so that all tools can achieve the highest placement rate. And the minimum number of vias. Since the OC48 processor bus uses an improved star topology, this has the highest priority during automatic routing.

After completion, the OC48 card layout board requires signal integrity verification and timing analogy The simulation results show that this method is feasible for PCB routing guidance to meet the expected requirements, and improves the timing quota of the second layer bus Finally, the design rule inspection, final manufacturing review, mask and review are sent to the manufacturer, and the layout task is officially ended

然后

聯系

電話熱線

13410863085Q Q

微信

- 郵箱