高速PCB設計中的串擾分析與控制

目前,日益成熟的半導體技術使得晶體管的尺寸越來越小,因此器件的信號跳變沿變得越來越快,導致高速數字領域的信號完整性和電磁兼容問題日益嚴重。 電路系統設計。 信號完整性問題主要包括傳輸線效應,如信號的反射、時延、振鈴、信號的過沖和下沖以及信號之間的串擾等。 其中,信號串擾最為復雜,涉及因素較多,計算復雜,控制難度大。 因此,當今的電子產品設計迫切需要有別于傳統設計環境、設計流程和設計方法的新的思路、流程、方法和技術。

EDA技術開發了一套用于高速PCB和電路板級系統的設計和分析工具和方法。 這些技術涵蓋了高速電路設計和分析的各個方面:靜態時序分析、信號完整性分析、EMI/EMC設計、地彈反射分析、功耗分析和高速路由器。 同時還包括信號完整性驗證和Sig''''n-Off、設計空間檢測、互連規劃、電氣規則約束的互連綜合,以及專家系統等技術方法,這也使得 高效、更好地解決信號完整性問題。 信號完整性分析與設計是高速PCB板級和系統級分析與設計的最重要手段。 它在硬件電路設計中發揮著越來越重要的作用。 在這里,我們將討論信號完整性中的信號串擾。

騷擾申請解決方案

由于信號間電磁場相互重合而產生的不需要的噪聲電壓信號稱為信號串擾。 如果串擾超過一定值,可能會導致電路故障,從而導致系統無法正常工作。 串擾問題可以從以下幾個方面解決:

a. 盡可能降低信號邊沿的轉換率

一般來說,在選擇器件時,在滿足設計指標的情況下,應盡量選擇慢速器件,并避免不同類型信號混合使用,因為快速轉換的信號對慢速轉換的信號存在潛在的串擾風險。

b. 采取屏蔽措施

為高速信號提供分組地是解決串擾問題的有效途徑。 但封裝用地會導致布線量增加,使原本有限的布線面積變得更加擁擠。 另外,為了達到地線屏蔽的預期目的,地線上接地點之間的距離至關重要,一般小于信號沿線變化長度的兩倍。 同時,地線也會增大信號的分布電容,使得傳輸線阻抗增大,信號邊沿變慢。

c. 合理設置層數和布線

合理設置布線層數和布線間距,減少平行信號線長度,縮短信號層與平面層間距,增大信號線間距,減少平行信號線長度(臨界長度范圍內)可以有效減少串擾。

d. 設置不同的路由層

對不同速率的信號設置不同的走線層數,合理設置平面層數也是解決串擾的好方法。

e. 阻抗匹配

如果傳輸線的近端或遠端阻抗與傳輸線阻抗匹配,串擾的幅度也可以大大降低。

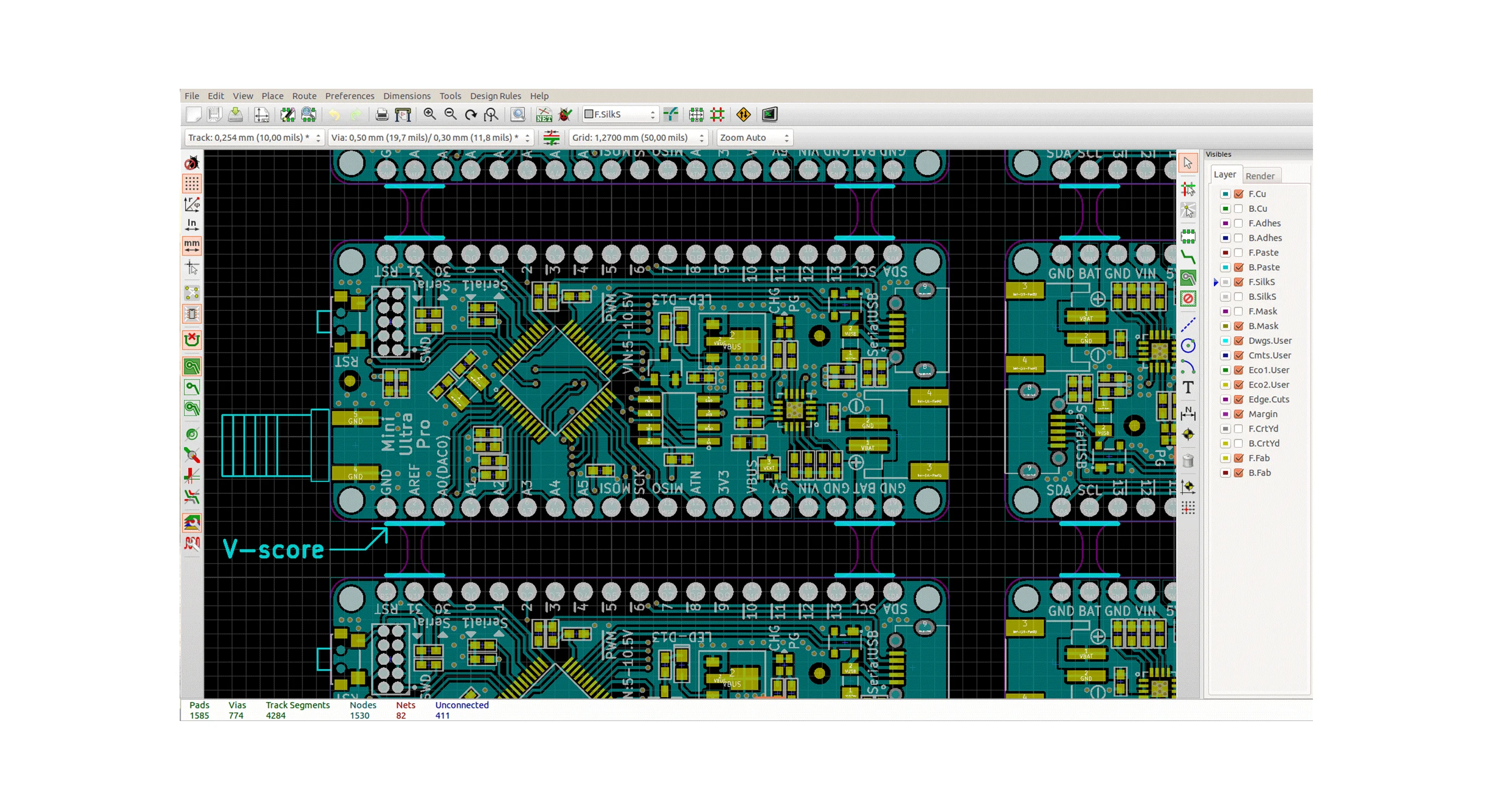

串擾分析的目的是快速發現、定位并解決PCB實現中的串擾問題。 通用仿真工具和環境仿真分析與PCB布線環境無關。 布線完成后,進行串擾分析,得到串擾分析報告。 導出新的接線規則并重新接線,然后進行分析和修正。 這種設計經常被重復。

通過仿真分析,我們可以看到實際的串擾結果是不同的,并且存在很大的差距。 因此,一個好的工具不僅應該分析串擾,還應該應用串擾規則進行路由。 另外,一般的布線工具僅由物理規則驅動,串擾控制的布線只能通過設置線寬、線距、最大并行布線長度等物理規則來約束。 使用信號完整性分析和設計工具集ICX可以支持真正意義上的電氣規則驅動布線。 其仿真分析和布線可以在一個環境中完成。 仿真時可以設置電氣規則和物理規則,布線時可以自動計算過沖、串擾等信號完整性要素,并根據計算結果自動修正布線。 接線速度快,真正滿足實際電氣性能要求。

串擾控制的信號完整性設計

高速PCB設計規則一般分為兩種:物理規則和電氣規則。 所謂物理規則是指根據設計工程師指定的物理尺寸而制定的某些設計規則,例如線寬為4Mi1、線間距為4Mi1、并行走線長度為4Mi1等。 電氣規則是指與電氣特性或電氣性能相關的設計規則,例如布線延遲控制在Ins和2ns之間,PCB上的串擾總量小于70mV等。

物理規則和電氣規則的定義可以進一步探索高速路由器。 目前,市場上基于物理規則(物理規則驅動)的高速路由器包括AutoActive RE路由器、CCT路由器、B1azeRouter路由器和Router Editor路由器。 事實上,這些路由器都是物理規則驅動的自動路由器,也就是說,它們只能自動滿足設計工程師指定的物理尺寸要求,并不直接受制于高速電物理尺寸的要求。 ,但不是由高速電氣規則直接驅動。

由電氣規則直接驅動的高速路由器對于保證高速設計信號的完整性非常重要。 設計工程師總是首先得到電氣規則,設計規范也是電氣規則。 換句話說,我們的設計。

然后

聯系

電話熱線

13410863085Q Q

微信

- 郵箱