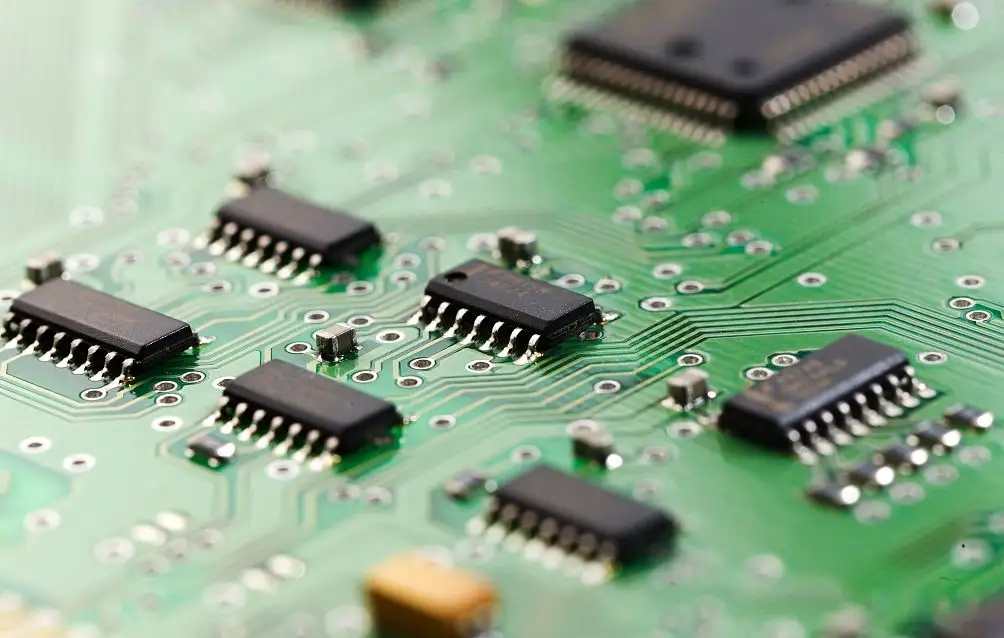

SDRAM原理設計及PCB設計布局規則

與傳統的SDRAM接口電路相比,注冊式SDARM電路對電路電參數的設計約束相對寬松,設計時基本不考慮主控芯片的驅動能力; 但由于Registered SDRAM也是一種高速接口電路,其電路設計也應遵循一定的規則,以保證所設計電路的可靠性和穩定性。

(一)原理設計規則

① 各芯片時鐘輸入端設計相位調整電容。 電容值可設置為10pF,可根據測量數據進行調整。

② 在每個SDRAM芯片的數據引腳中,串聯設計了匹配電阻。 匹配電阻值可設置為l0Ω。

③ 每個鎖存器芯片的鎖存時鐘使用時鐘擴展電路的不同輸出時鐘。

④ 每個SDRAM芯片的輸入時鐘采用不同的時鐘擴展電路的輸出時鐘。

⑤ 在時鐘擴展芯片的時鐘輸出引腳處設計串聯匹配電阻。 匹配電阻值可設置為l0Ω。

⑥ 鎖存器芯片的輸出端設計有串接匹配電阻。 匹配電阻值可設置為lOΩ。

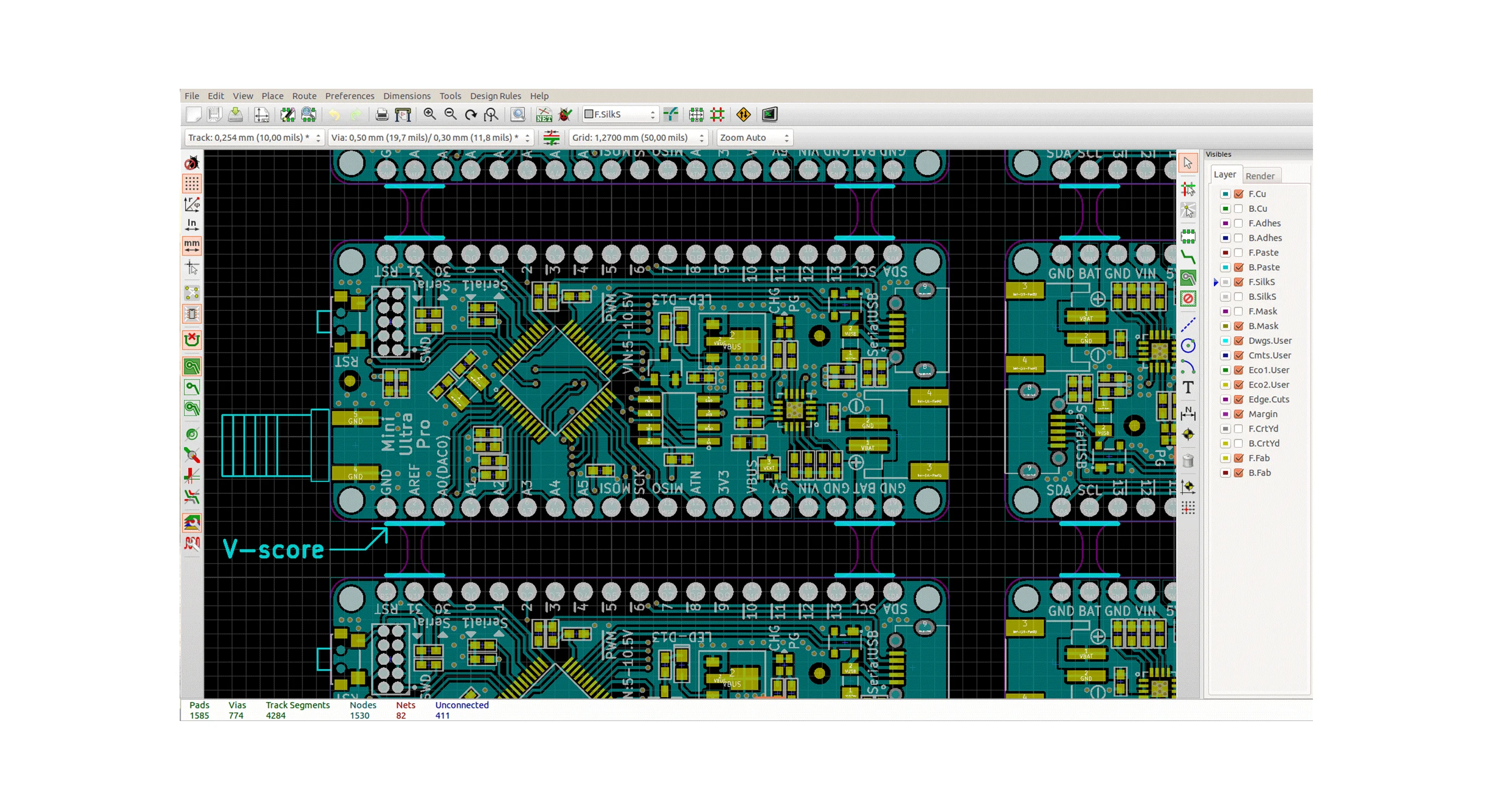

(二) 主板走線規則

① SDRAM數據線:從MPC824l到同一SDRAM芯片的數據信號走線需要控制等長,長度誤差控制在±5%以內。

② SDRAM地址/控制線:鎖存芯片到SDRAM芯片的地址/控制信號走線需控制等長,長度誤差應控制在±5%以內。

③時鐘擴展電路輸出2路鎖存時鐘給鎖存芯片。 其走線需控制等長,長度誤差控制在±27mm以內。

④時鐘擴展電路輸出4路時鐘到SDRAM芯片,其走線需要控制等長,長度誤差控制在±1 27 mm以內。

⑤鎖存器芯片到SDRAM芯片的地址/控制信號與時鐘擴展電路到對應SDRAM芯片的時鐘線長度基本相同,長度誤差控制在±5%以內。

⑥時鐘擴展電路的反饋時鐘走線長度基本等于時鐘擴展電路到SDRAM芯片的平均時鐘走線長度,長度誤差控制在±10%以內。

⑦MPC824l與SDRAM芯片之間的數據線、地址線、控制線、時鐘線的走線長度基本相等,長度誤差控制在±10%以內。

(三)布局規則

① 所有調相電容均置于接收端附近。

② 所有時鐘串聯匹配電阻均靠近發送端放置。

③SDRAM芯片數據引腳的串行匹配電阻靠近SDRAM芯片。

④鎖存芯片輸出端串聯匹配電阻靠近輸出端放置。

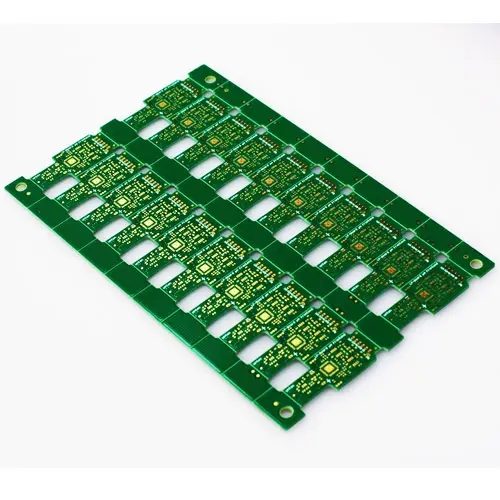

(四)其他設計規則

① 每根接線均進行阻抗控制,即單端線采用50Ω阻抗。

②芯片的電源引腳必須配備去耦電容,電容值為O一μF。原則上每個電源引腳都必須設計去耦電容,并盡可能靠近電源引腳布置。

③ 完整的地層和供電層至少應保證地層完整。

④時鐘信號盡量走內層,以減少EMI。

(五)設計電路的調試

按照上述規則設計的硬件PCB電路只需稍微調整相位調整電容即可穩定工作在100 MHz SDRAM時鐘下。 調相電容的范圍一般為5~15pF。 如果定時參數余量足夠,調相電容也可以不焊接。

然后

聯系

電話熱線

13410863085Q Q

微信

- 郵箱