電子廠電路板設計硬件布局經驗

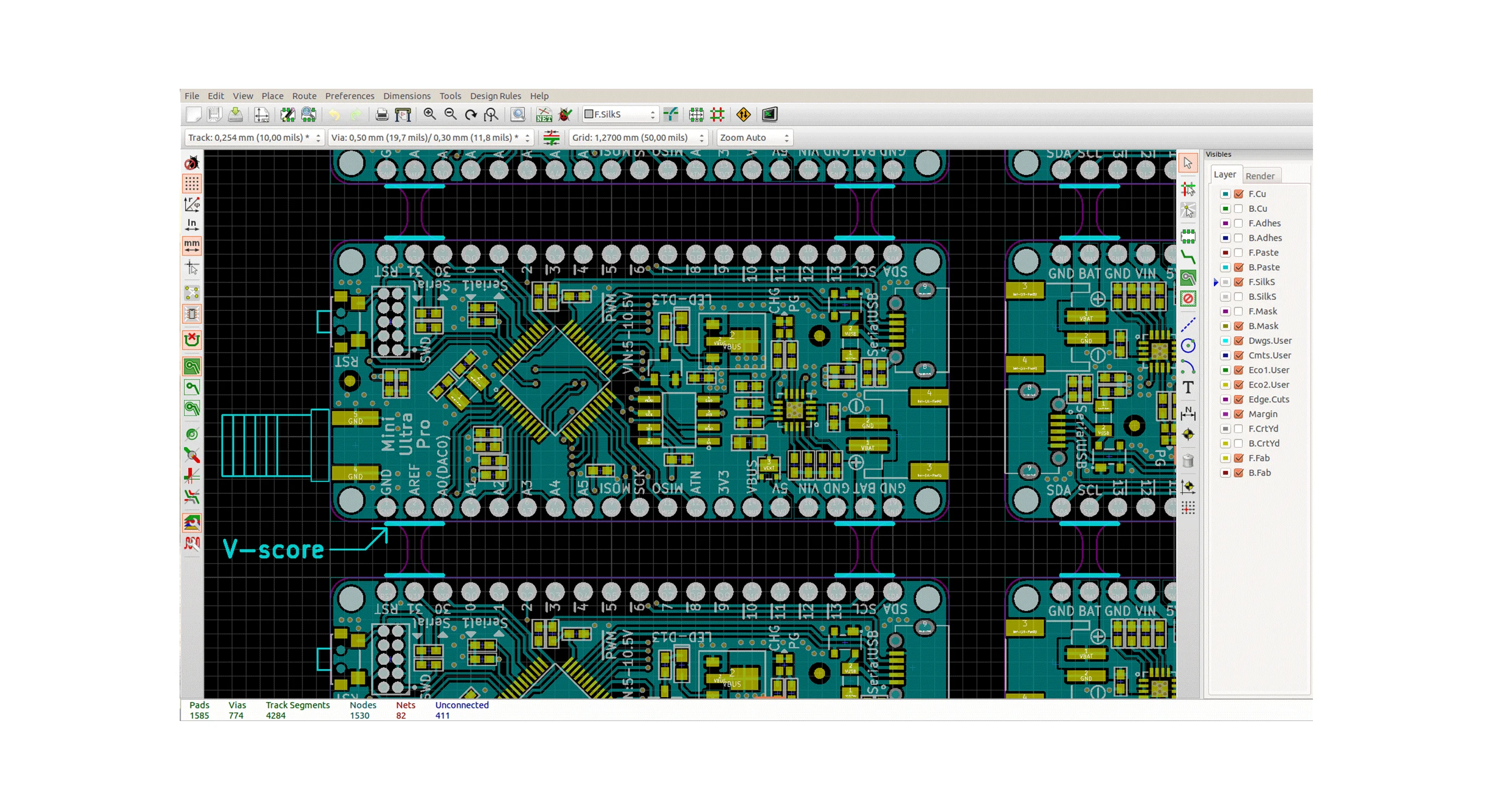

時鐘電纜布線

1、表層無時鐘走線或走線長度=<500mil(關鍵時鐘表層走線=<200mil); 另外,應使用完整的地平面作為返回電流,未分割或分離的位置應進行橋接。

2、晶振和時鐘驅動電路區TOP層無其他走線; (這有時很難滿足。)。

3、信號線周圍應避免其他信號線,必要時滿足3W原則(兩線中心距為線寬的3倍)。 布置數據線或地址線時一般不考慮這一點,但強調時序(等長)。

4、如有可能,供電層應盡量滿足20h原則:即供電層邊界為地層邊界內收縮板厚度的20倍。

20H規則:由于電源層與地層之間的電場是變化的,電磁干擾會在板子邊緣輻射。 這稱為邊緣效應。 電源層可以縮小,使得電場僅在接地層的范圍內傳導。 以1H(電源與地之間介質的厚度)為單位,減少20H即可將70%的電場限制在接地邊緣; 縮小100H可以限制98%的電場。

5、不同頻率的時鐘滿足3W原則

3W規則:為了減少線路之間的干擾,保證線路間距足夠大。 當線中心距不小于3倍線寬時,70%的電場不能相互干擾,稱為3W規則。 如果98%的電場不互相干擾,則可以使用10W規則。

6、當時鐘信號層改變,返回參考面也改變時,一般在時鐘線層改變孔旁邊設置接地孔。

7、時鐘線與I/O接口、手柄距離≥1000mil。

8、時鐘線與相鄰平面層走線等長<=1000mil。

9、多負載時鐘結構盡量采用星形。 實際實施中,一般采用走到多負載點相對中心時進行等長分叉。

10、在SDRAM布線中,SDCLK和DATA之間的長度差<=800mil。

11、帶狀線(中層走線)典型傳輸速度為180ps/英寸,微帶線(表層走線)典型傳輸速度為140ps/英寸。

接口接線要求:

1、差異分布線規則:平行等距、同層、等長。

2、接口變壓器與接口連接器之間的網絡長度小于1000ml。

3、跨分區的復位線應采取架橋措施。

4、接口電路的接線應遵循先保護后濾波的原則。

5、接口變壓器、光耦等初級和次級隔離器件相互隔離,無相鄰平面等耦合路徑,對應參考平面的隔離寬度大于100mil。

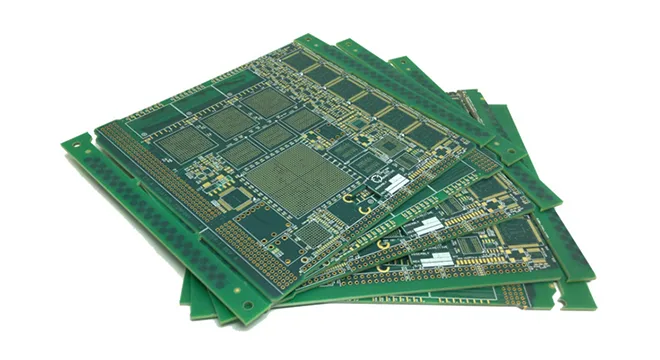

板的堆疊:

1、元件層的相鄰層為地平面,為器件屏蔽層和固定層布線層提供參考平面。

2、所有信號層應盡可能靠近地平面。

3、 盡量避免兩個信號層直接相鄰。

4、主電源應盡量靠近其相應的地。

5、考慮疊層結構的對稱性。

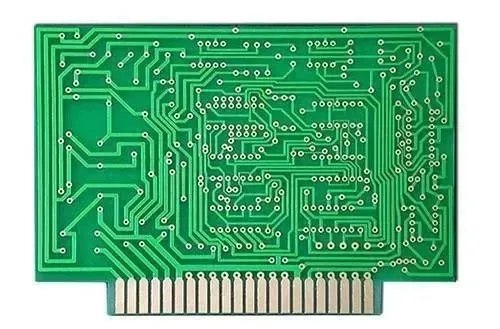

其他接線注意事項:

1、供電層與地層之間的EMC環境較差,應避免對干擾敏感的信號。

2、信號線不能有直角。

3、布線應盡量靠近一個平面,避免交叉分割。 如果需要交叉劃分或者不能靠近電源地平面,這些情況只允許存在于低速信號線中。

然后

聯系

電話熱線

13410863085Q Q

微信

- 郵箱