你知道PCB電路板的EMI是多少嗎? pci電路板emi設計規范的原則有哪些?

1、IC的供電處理

1.1)確保每個IC的電源PIN都有一個0.1UF的去耦電容。 對于BGA chip,BGA的四個角需要8顆0.1UF和0.01UF的電容。 PCB走線的供電要特別注意加濾波電容,比如VTT。 這不僅會影響穩定性,還會影響 EMI。

2.時鐘線處理

2.1)建議先走時鐘線。

2.2)對于頻率大于等于66M的時鐘線,每條線的過孔數不超過2個,平均不超過1.5個。

2.3)頻率小于66M的時鐘線,每條線的過孔數不超過3個,平均不超過2.5個

2.4)長度大于12inch的時鐘線,如果頻率大于20M,過孔數不超過2個。

2.5)如果時鐘線有過孔,在過孔相鄰位置的第二層(stratum)和第三層(power layer)之間加旁路電容,保證參考層的高頻電流環路( 相鄰層)在時鐘線改變后是連續的。 旁路電容所在的電源層必須是過孔穿過的電源層,并盡可能靠近過孔。 旁路電容器和過孔之間的最大距離不應超過 300 MIL。

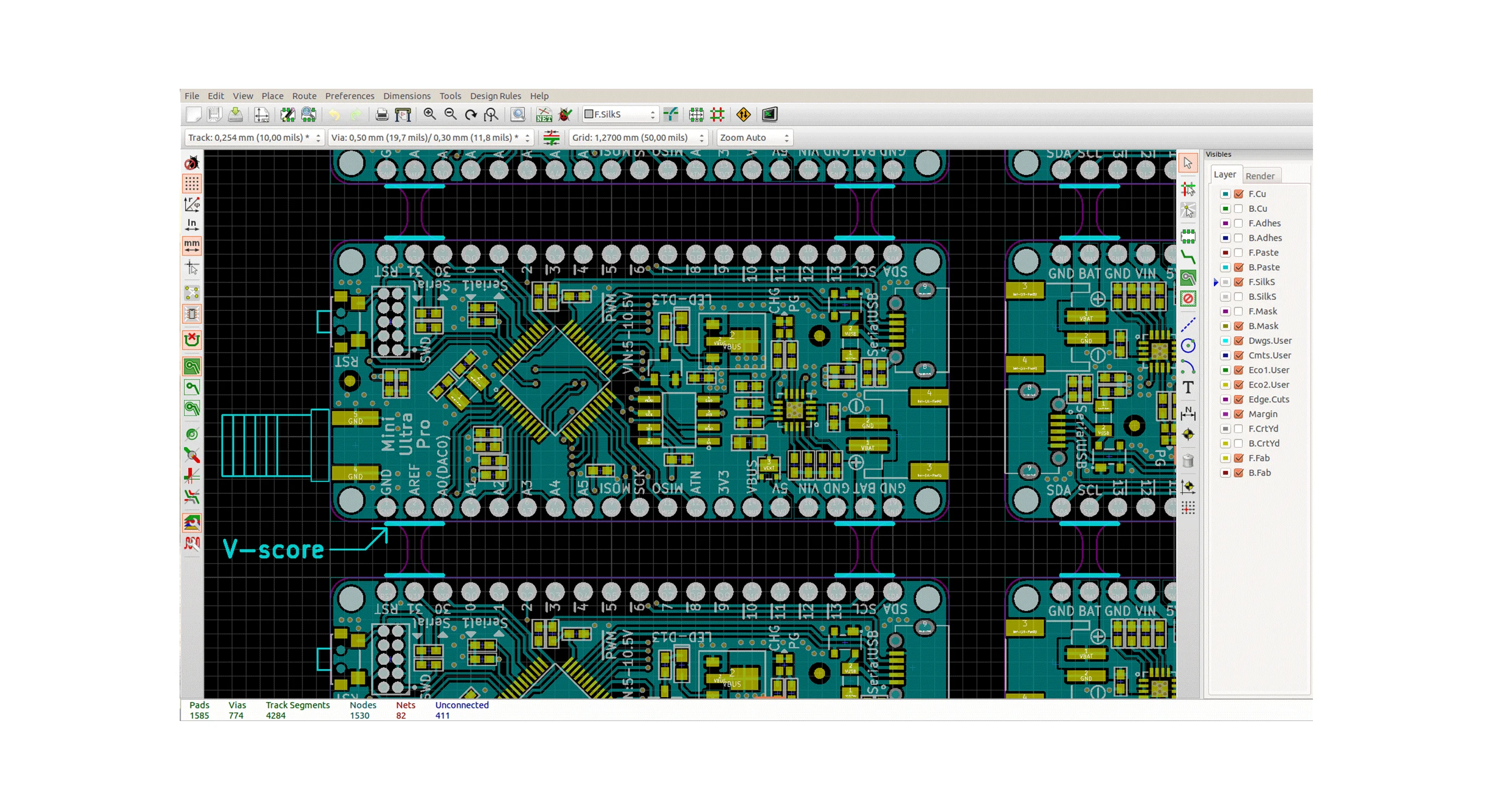

2.6) 所有時鐘線路原則上不得跨島。 這里有四個跨島案例。

2.6.1) 跨島發生在電源島與電源島之間。 此時時鐘線走在第四層的背面PCB上。 第三層(電源層)有兩個電源島,第四層的PCB走線必須穿過這兩個島。

2.6.2) 電源島和地島之間出現跨島。 此時時鐘線走在第四層的背面PCB上。 第三層(電源層)的電源島中間有一個接地島,第四層的PCB走線必須穿過這兩個島。

2.6.3) 島穿越發生在地島和地層之間。 此時時鐘線走在第一層PCB上,第二層(stratum)中間有一個地島,第一層PCB的走線必須穿過地島,即 相當于地線斷了。

2.6.4)時鐘線下不鋪銅。 如果條件限制,頻率大于等于66M的時鐘線不能跨島。 如果頻率小于66M的時鐘線跨島,必須加去耦電容形成鏡像通路。 在兩個電源島之間并靠近跨島時鐘線放置一個 0.1UF 電容。

2.7) 當有兩個過孔和一個島穿越的選擇時,選擇一個島穿越。

2.8) 時鐘線距離I/O側板邊500MIL以上,不得與I/O線走線。 如果做不到,時鐘線和I/O端口線之間的距離應大于50 MIL。

2.9)當時鐘線走在第四層時,時鐘線的參考層(電源平面)應盡量在給時鐘供電的電源平面上。 以其他電源平面為參考的時鐘越少越好。 另外,頻率大于或等于66M的時鐘線的參考電源平面必須是3.3V電源平面。

2.10) 時鐘線之間的距離應大于 25 MIL。

2.11)時鐘線的進線和出線要盡量遠。 盡量避免類似的線程方法,。

2.12)時鐘線連接BGA等器件時,如果時鐘線換層,盡量避免使用PCB走線形式。 BGA下面不要走過孔,最好使用H PCB走線形式。

2.13)注意所有時鐘信號,不要忽略任何時鐘,包括AUDIO CODEC的AC_特別注意FS3-FS0。 雖然它的名字不是時鐘,但它實際上是一個時鐘。

2.14) Clock chip的上拉和下拉電阻盡量靠近Clock Chip。

3. I/O口處理

3.1)每個I/O口,包括PS/2、USB、LPT、COM、SPEAK OUT和GAME,都分成一塊地,最左邊和最右邊接數字地,寬度不小于 200MIL或者三個過孔,其他地方不接數字地。

3.2) 如果COM2口是pin型的,盡量靠近I/O地。

3.3) I/O電路EMI設備應盡可能靠近I/O SHIELD。

3.4) 供電層和I/O口處的地層隔離成孤島,Bottom和TOP層鋪好,信號不跨島(信號線直接從PORT引出 , 不允許在 I/O PORT 進行長距離 PCB 走線)。 給出了I/O口處理的參考。

四、注意事項

A. PCB設計工程師應嚴格遵守EMI PCB設計規范。 EMI工程師有權檢查。 PCB設計工程師應對因違反EMI PCB設計規范而導致的EMI測試失敗負責。

B、EMI工程師負責PCB設計規范,嚴格遵守EMI PCB設計規范,但仍未通過EMI測試。 EMI工程師負責提供解決方案,并匯總在EMI PCB設計規范中。

C、EMI工程師負責每個外設端口的EMI測試,不得遺漏測試。

D、每位PCB設計工程師均有權對PCB設計規范提出建議和質疑。 EMI工程師負責解答問題,通過實驗確認工程師的建議后,增加PCB設計規范。

E. EMI工程師負責降低EMI PCB設計成本,減少磁珠的使用數量。

然后

聯系

電話熱線

13410863085Q Q

微信

- 郵箱