PCB設計中數字電路和單片機的抗干擾設計

在電子系統設計中,為了少走彎路、節省時間,應充分考慮并滿足抗干擾要求,避免設計完成后針對抗干擾采取補救措施。形成干擾的基本要素有3個:

(1)干擾源是指產生干擾的部件、設備或信號。用數學語言描述為:du/dt,其中di/dt較大,為干擾源。例如雷電、繼電器、可控硅、電機、高頻時鐘等都可能成為干擾源。

(2)敏感設備是指容易受到干擾的物體。如:A/D、D/A轉換器、單片機、數字IC、弱信號放大器等。

(3)傳播路徑是指干擾從干擾源傳播到敏感設備所經過的路徑或介質。典型的干擾傳播路徑是通過電線傳導并從空間輻射。

抗干擾設計的基本原則是抑制干擾源,切斷干擾傳播路徑,提高敏感器件的抗干擾性能。(類似傳染病的預防)

1.抑制干擾源

抑制干擾源就是盡可能減少干擾源的du/dt、di/dt。 這是抗干擾設計中最優先、最重要的原則,往往可以達到事半功倍的效果。 降低干擾源的du/dt主要是通過在干擾源兩端并聯電容來實現的。通過在干擾源電路中串聯電感或電阻以及續流二極管來降低干擾源的di/dt。

抑制干擾源的常用措施有:

(1) 布線時避免使用90度折線,以減少高頻噪聲發射。

(2)繼電器線圈加續流二極管,消除線圈斷開時產生的反電動勢干擾。僅增加續流二極管會延遲繼電器的斷開時間,并且增加穩壓二極管后繼電器可以在單位時間內動作更多次。

(3)在繼電器觸點兩端并聯火花抑制電路(一般為RC串聯電路,電阻為K到幾十K,電容為0.01uF),以減少電火花的影響。

(4)給電機加濾波電路,注意電容、電感引線盡量短。

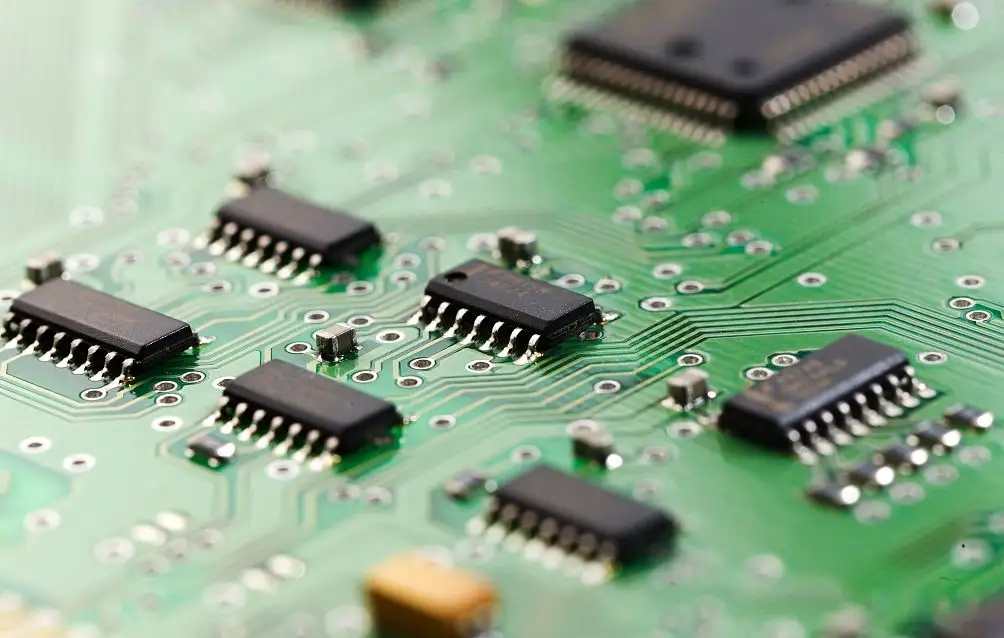

(5)電路板上的每個IC均需并聯0.01μF~0.1μF高頻電容,以減少IC對電源的影響。注意高頻電容的接線。接線應靠近電源端子且盡可能短。否則會增大電容器的等效串聯電阻,影響濾波效果。

(6)在晶閘管兩端并聯RC抑制電路,以降低晶閘管產生的噪聲(噪聲嚴重時,可能會擊穿晶閘管)。根據干擾的傳播路徑,可分為傳導干擾和輻射干擾。

所謂傳導干擾是指通過導線傳輸到敏感設備的干擾。高頻干擾噪聲的頻帶與有用信號的頻帶不同。可以通過在線路上加濾波器來截斷高頻干擾噪聲的傳輸。有時,可以添加隔離光耦來解決這個問題。電源噪聲的危害性最大,因此應特別注意處理。所謂輻射干擾是指通過空間輻射傳輸到敏感設備的干擾。一般的解決辦法是增加干擾源與敏感器件之間的距離,用地線隔離,并在敏感器件上加屏蔽層。

2.切斷干擾傳播路徑的常用措施有:

(1)充分考慮電源對MCU的影響。如果電源做得好,整個電路的抗干擾就解決了一大半。許多單片機對電源噪聲非常敏感。為了減少電源噪聲對單片機的干擾,應在單片機的電源中添加濾波電路或穩壓器。例如,可以采用磁珠和電容器組成π形濾波電路。當然,條件不要求時也可以用100Ω電阻來代替磁珠。

(2)如果單片機的I/O口用于控制電機等噪聲器件,則I/O口與噪聲源之間應加隔離(應加π濾波電路)。控制電機等噪聲設備時,I/O口與噪聲源之間需加隔離(加π濾波電路)。

(3)注意晶振接線。晶振盡量靠近單片機引腳,時鐘區域用地線隔離。晶振外殼應接地并固定。這項措施可以解決很多難題。

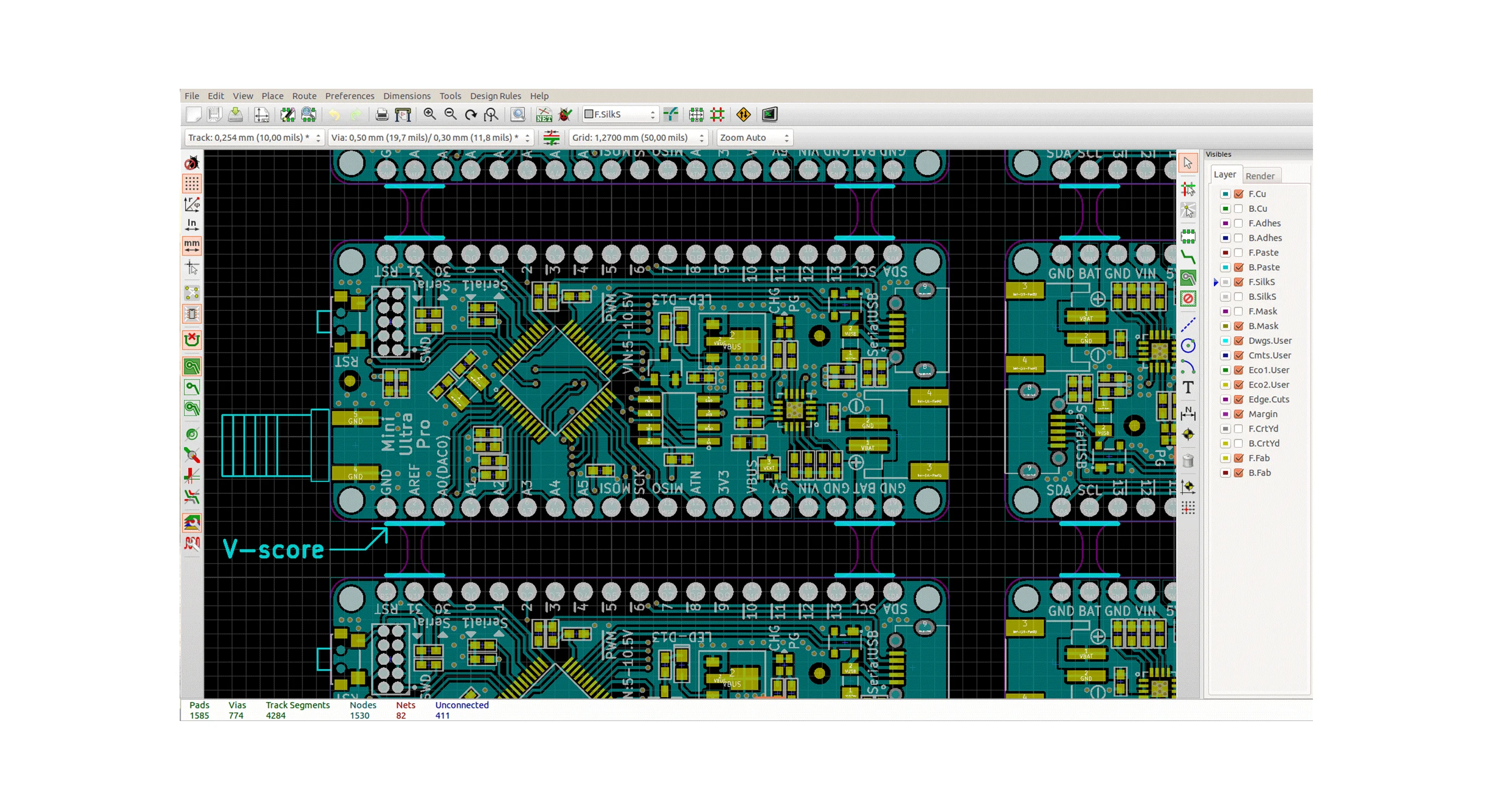

(4)電路板應合理分區,如強弱信號、數字信號和模擬信號等。 盡量使干擾源(如電機、繼電器)遠離敏感元件(如單片機)。

(5) 數字區與模擬區用地線隔離。數字地與模擬地分開,最后一點連接到電源地。A/D和D/A芯片的接線也是基于這個原理。制造商在分配A/D和D/A芯片的管腳排列時已經考慮到了這一要求。

(6)單片機與大功率器件的地線應分別接地,以減少相互干擾。大功率器件應盡量放置在電路板的邊緣。

(7)單片機的I/O口、電源線、電路板連接線等關鍵區域采用磁珠、磁環、電源濾波器、屏蔽罩等抗干擾元件,可顯著提高抗干擾能力。電路的抗干擾性能。

3.提高敏感器件的抗干擾性能

提高敏感器件的抗干擾性能是指盡量減少干擾噪聲的拾取并從異常狀態中恢復的方法。

然后

聯系

電話熱線

13410863085Q Q

微信

- 郵箱