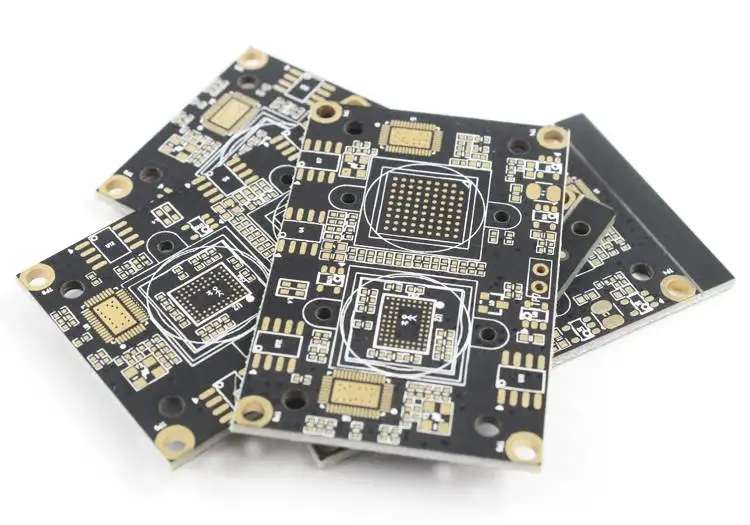

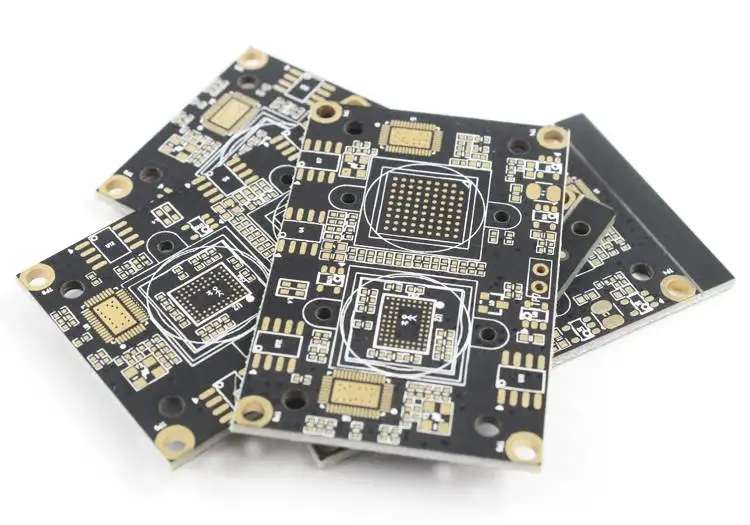

PCB電路板設計共模干擾對地放電的解決方案

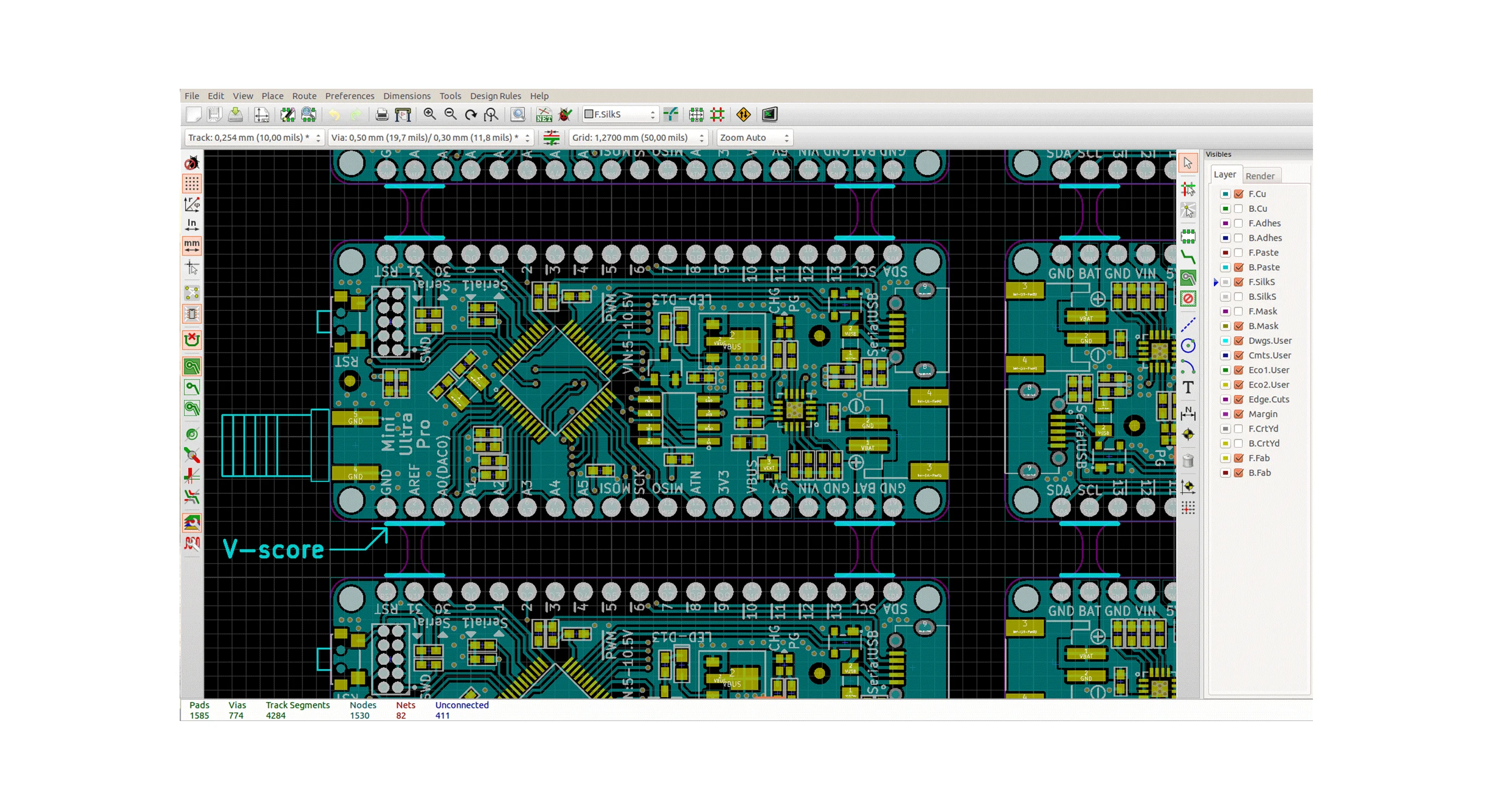

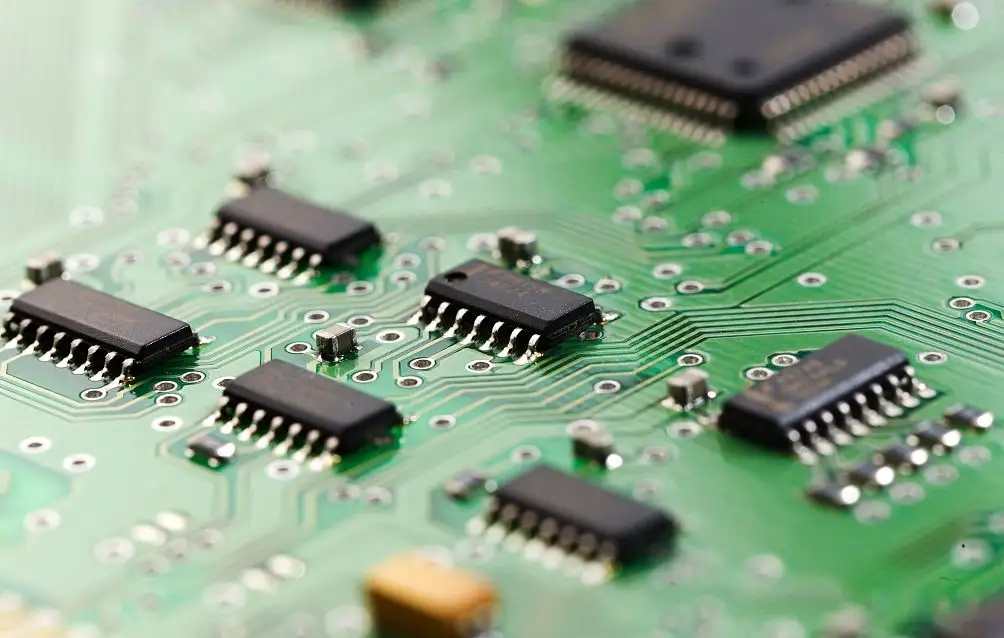

印制電路板的設計是根據電路原理圖來實現電路設計者所需要的功能。 印制電路板的設計主要是指布局設計,需要考慮外部連接的布局。 內部電子元件的優化布局、金屬布線和過孔的優化布局、電磁防護、散熱等因素。 優秀的布局設計可以節省生產成本并實現良好的電路性能和散熱。 簡單的版圖設計可以通過手工實現,而復雜的版圖設計則需要通過計算機輔助設計(CAD)來實現。

如何解決共模干擾對地放電? 其中,有網友提出“一漏”、“二堵”。 什么叫“一漏”“二堵”? 詳情請參閱下文。

“二合一”觀點:

1、對于接地產品,當然希望將電纜傳導的共模干擾通過電容或瞬態抑制器件引導至大地或機箱,防止其對敏感電路(如CPU)產生干擾。

2、對于浮地產品,主要通過串聯磁環(或增加共模阻抗)防止共模電壓轉為差模電壓對敏感電路產生干擾; 其次,要注意PCB布線,不僅要使PCB的各電路對其參考地(數字地GND,而不是接地產品的機箱地PG)保持零電位,還要將其放置在PCB的濾波電路中。 I/O、RST、CS(片選)等關鍵信號。 這樣,無論共模干擾有多嚴重,都不會干擾數字電路。

3、第一種方法是放電(吳老師說的,但是需要良好的接地或者金屬外殼),第二種方法是阻斷(第二種方法解釋的,避免共模干擾轉化為差模干擾,這樣 影響電路)。 第一種方法主要用于接地良好的地面設備(如通信基站),第二種方法主要用于機載、機載和船載設備。

4、當然,人們會說第二種方法(浮地)可能由于PCB板與地之間的寄生電容而無法應對高頻干擾。 但對于鐵路、電力和工業控制場所來說,主要干擾是變頻器、大功率電機、斷路器或開關,產生的干擾主要是10MHZ以上。 另外,地線干擾(強電短路、雷擊、諧波、漏電流)也極其嚴重且不穩定(一般可達0.8V)。 對于一些關鍵CPU的1.2V工作電壓來說,簡直是魔鬼啊!

5、高頻共模電磁干擾的能量一般不大。 比如手機和大功率RFID(我體驗的最大功率只有3W)。 因為是高頻,鐵氧體磁環或磁珠可以吸收,金屬外殼(或塑料外殼內噴涂的導電涂層)可以完全反射或吸收——現在鐵路要求800~1000M,1.4G~2.1G 輻射抗擾度測試(最高20V/M),以及2.1G~2.5G輻射抗擾度測試(最高5V/M),所以設備幾乎沒有問題。 當然,設備還要通過CS、ESD、EFT等測試。

網友看法:

對于外部共模干擾的解決辦法,我很同意華二雄的觀點。 至于寄生電容對高頻干擾的影響,個人經驗,這并不是什么大問題。 意見如下:

實際運行中,對系統危害最大的因素是低頻共模干擾,如華二雄提到的大功率電機、斷路器或開關、短路、雷電感應等。 這些類型大多是外部共模信號,其脈沖寬度從數百us到s,最長周期也為數秒。 此類脈沖不斷對地造成高電壓波動,從而損壞系統。 但對于高頻共模干擾,從干擾源開始,大部分能量都是以輻射的形式傳輸的,而這種共模干擾大多發生在系統本身。

您對此有何看法,或者還有其他更好的解決方案嗎?

---- 電路板組裝、電路板設計、電路板加工廠家講解如何解決PCB電路板設計中的共模干擾對地放電。

然后

聯系

電話熱線

13410863085Q Q

微信

- 郵箱