PCB工程師詳細講解基于EMC的PCB設(shè)計

簡介

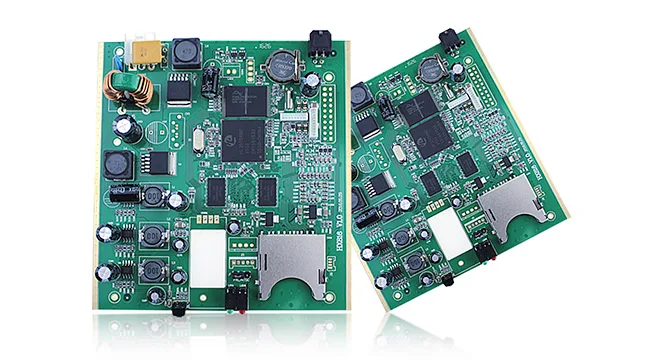

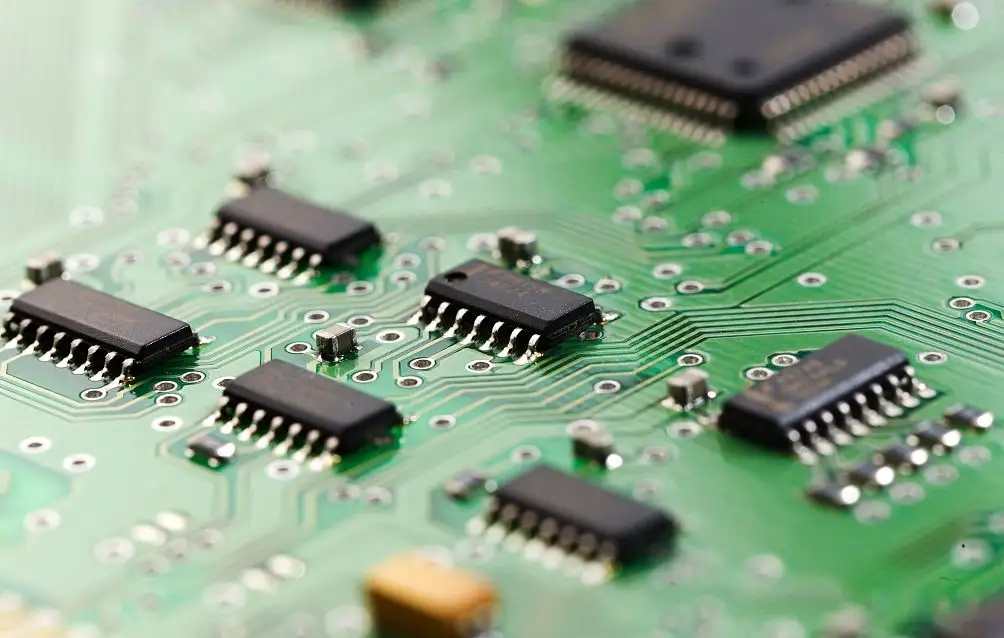

PCB是英文printed circuit board的縮寫。 一般來說,印刷電路是指按照預(yù)定設(shè)計在絕緣材料上由印刷電路、印刷元件或兩者制成的導(dǎo)電圖案。 在絕緣基板上提供元件之間電氣連接的導(dǎo)電圖案稱為印制電路。 這樣,印制電路或印制電路的成品板就稱為印制電路板,也稱為印制板或印制電路板。 幾乎所有我們能看到的電子設(shè)備都離不開PCB,從電子表、計算器和通用計算機到計算機、通訊電子設(shè)備、航空、航天和軍用武器系統(tǒng)。 只要有集成電路和其他電子元件,PCB就用于它們之間的電氣互連。 其性能直接關(guān)系到電子設(shè)備的質(zhì)量。 隨著電子技術(shù)的飛速發(fā)展,電子產(chǎn)品越來越趨于高速、高靈敏度、高密度。 這種趨勢導(dǎo)致了PCB設(shè)計中電磁兼容性(EMC)和電磁干擾的嚴重問題。 EMC設(shè)計已成為PCB設(shè)計中亟待解決的技術(shù)問題。

1 電磁兼容性

電磁兼容性(EMC)是一門新興的綜合學科,主要研究電磁干擾和抗干擾。 電磁兼容性是指在規(guī)定的電磁環(huán)境水平下,電子設(shè)備或系統(tǒng)不會因電磁干擾而降低其性能指標,同時其產(chǎn)生的電磁輻射不會超過限定的限值水平,不會影響電子設(shè)備或系統(tǒng)的性能。 保證其他系統(tǒng)的正常運行,達到設(shè)備與系統(tǒng)之間互不干擾、可靠工作的目的。 電磁干擾(EMI)是由電磁干擾源通過耦合路徑將能量傳輸?shù)矫舾邢到y(tǒng)引起的。 它包括三種基本形式:電線和公共地線傳導(dǎo)、空間輻射或近場耦合。 實踐證明,即使電路原理圖設(shè)計正確,印刷電路板設(shè)計不當,也會對電子設(shè)備的可靠性產(chǎn)生不利影響,因此保證印刷電路板的電磁兼容性是整個系統(tǒng)設(shè)計的關(guān)鍵 。

1.1 電磁干擾(EMI)

當EMI問題出現(xiàn)時,需要用三個要素來描述:干擾源、傳播路徑和接收器。因此,如果我們想要減少電磁干擾,就需要想辦法處理這三個要素。 現(xiàn)在我們主要討論印刷電路板的布線技術(shù)。

2 印制電路板的布線技術(shù)

良好的 PCB 布線是 EMC 的一個非常重要的因素。

2.1 PCB的基本特性

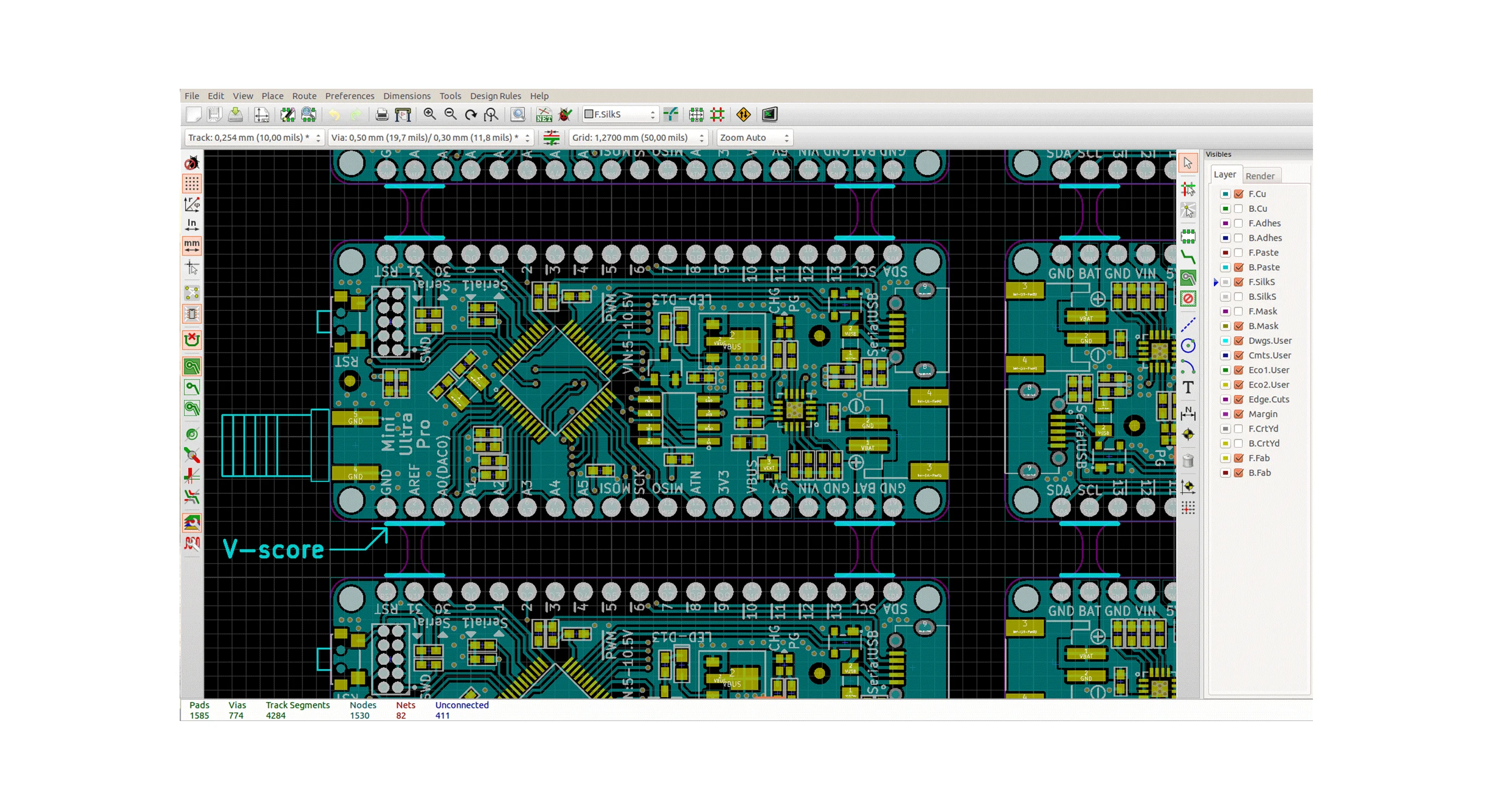

PCB由垂直堆疊上的一系列層壓、布線和預(yù)浸處理組成。 在多層PCB中,設(shè)計者會將信號線布在最外層,以方便調(diào)試。PCB上的布線具有阻抗、電容和電感特性。

阻抗:布線的阻抗由銅的重量和橫截面積決定。 例如,一盎司銅的阻抗為 0.49 m Ω/單位面積。 電容:布線的電容由絕緣體(EoEr)、電流范圍(A)和布線間距(h)決定。 方程表示為C=EoErA/h,Eo是自由空間的介電常數(shù)(8.854 pF/m),Er是PCB基板的相關(guān)介電常數(shù)(FR4軋制中為4.7)。

電感:布線的電感均勻分布在布線中,約為1nH/m。

對于1盎司的銅線,在0.25mm(10mil)厚的FR4的軋制條件下,接地層上方0.5mm(20mil)寬、20mm(800mil)長的導(dǎo)線可產(chǎn)生9.8mΛ的阻抗, 電感為 20 nH,與地耦合電容為 1.66 pF。 將上述值與元件的寄生效應(yīng)進行比較,這些可以忽略不計,但所有布線的總和可能超過寄生效應(yīng)。 因此,設(shè)計者必須考慮到這一點。 PCB 布線的一般準則:

(1)增加導(dǎo)線之間的距離,減少電容耦合的串擾;

(2)電源線和地線平行分布,優(yōu)化PCB電容;

(3)敏感高頻線應(yīng)遠離高噪聲電源線;

(4)加寬電源線和地線,降低電源線和地線的阻抗。

2.2 細分

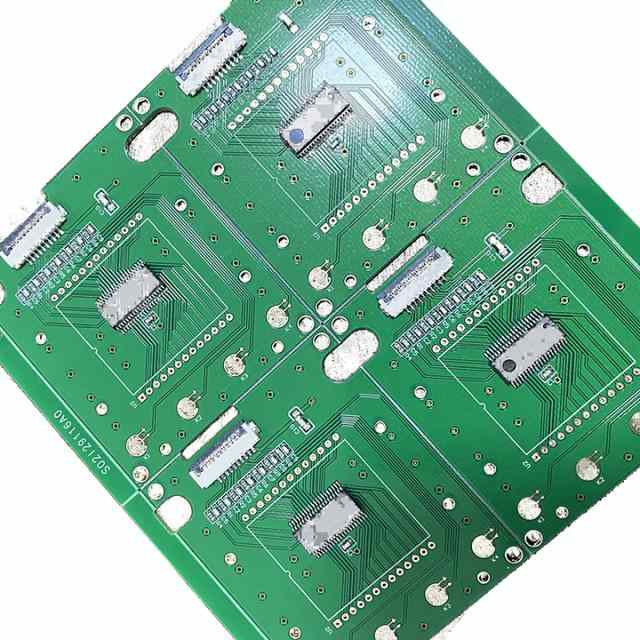

劃分是指物理上的劃分,以減少不同類型線路之間的耦合,特別是通過電源線和地線。

使用劃分技術(shù)劃分 4 種不同類型電路的示例。 在接地平面上,使用非金屬溝槽來隔離四個接地平面。 L和C作為電路板各部分的濾波器,以減少不同電路的電源面之間的耦合。 高速數(shù)字電路因其較高的瞬時功率需求而需要放置在電源入口處。 接口電路可能需要用于靜電放電(ESD)和瞬態(tài)抑制的器件或電路。 對于L和C,最好使用不同的L和C值,而不是使用一個大的L和C,因為這樣可以為不同的電路提供不同的濾波特性。

2.3 本地電源與IC之間的去耦

局部去耦可以減少沿電源的噪聲傳播。 連接在電源輸入端口和PCB之間的大容量旁路電容充當?shù)皖l紋波濾波器,并作為潛在的存儲來滿足突然的電源需求。 另外,每個IC的電源和地之間應(yīng)該有去耦電容。 這些去耦電容應(yīng)盡可能靠近引腳。 這將有助于過濾 IC 的開關(guān)噪聲。

2.4 接地技術(shù)

接地技術(shù)適用于多層PCB和單層PCB。 接地技術(shù)的目標是最小化接地阻抗,從而降低從電路回到電源的接地環(huán)路的電勢。

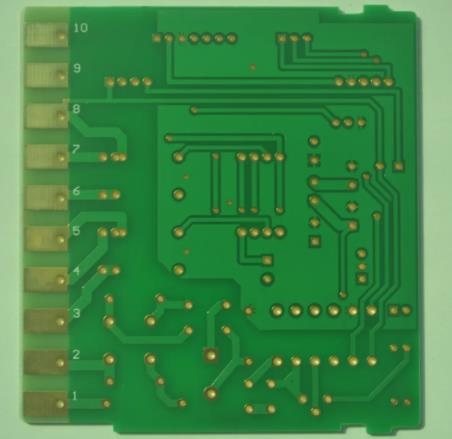

(1)單層PCB的地線

在單層(單面)PCB中,接地線的寬度應(yīng)盡可能寬,至少為1.5毫米(60密爾)。 由于星形布線無法在單層PCB上實現(xiàn),因此跳線和地線寬度的變化應(yīng)保持在最小限度,否則線路阻抗和電感將發(fā)生變化。

(2)雙層PCB的接地線

在雙層(雙面)PCB中,數(shù)字電路優(yōu)先采用地網(wǎng)格/點陣布線,這樣可以減少地阻抗、地環(huán)路和信號環(huán)路。 單層PCB中,地線和電源線的寬度至少為1.5mm。 另一種布局是將接地層放置在一側(cè),將信號線和電源線放置在另一側(cè)。 在這種布置中,接地電路和阻抗將進一步減小,并且去耦電容可以盡可能靠近IC電源線和地平面放置。

(3) 保護環(huán)

保護環(huán)是一種接地技術(shù),可以隔離環(huán)外的噪聲環(huán)境(如射頻電流),因為正常工作時沒有電流流過保護環(huán)。

(4)PCB電容

在多層板上,PCB電容是由將電源表面與地分開的薄絕緣層產(chǎn)生的。 在單層板上,電源線和地線的平行敷設(shè)也會導(dǎo)致這種電容效應(yīng)。 PCB電容器的優(yōu)點之一是它具有非常高的頻率響應(yīng)和均勻分布在整個表面或整條線路上的低串聯(lián)電感。 相當于整個板上均勻分布的去耦電容。 沒有任何一個分立元件具有此功能。

(5)高速電路和低速電路

高速電路應(yīng)靠近地面布置,低速電路應(yīng)靠近電源面布置。

(6)地面填銅

在一些模擬電路中,未使用的電路板區(qū)域被大片地覆蓋,以提供屏蔽并增加去耦能力。 但是,如果銅區(qū)域是懸空的(例如,沒有接地),則可能會充當天線并導(dǎo)致電磁兼容性問題。

(7) 多層PCB中的接地層和電源層

在多層PCB中,接地層和電源層通常都是平面銅區(qū)域,它們覆蓋整個內(nèi)部層,以提供均勻的地和電源分布。這有助于提高信號完整性、降低電路的噪聲水平,并簡化PCB布線。同時,良好的接地層和電源層布局可以減少電磁干擾,提高電路的抗干擾能力。

然后

聯(lián)系

電話熱線

13410863085Q Q

微信

- 郵箱