電路板廠經驗總結講解DDR2 PCB布局

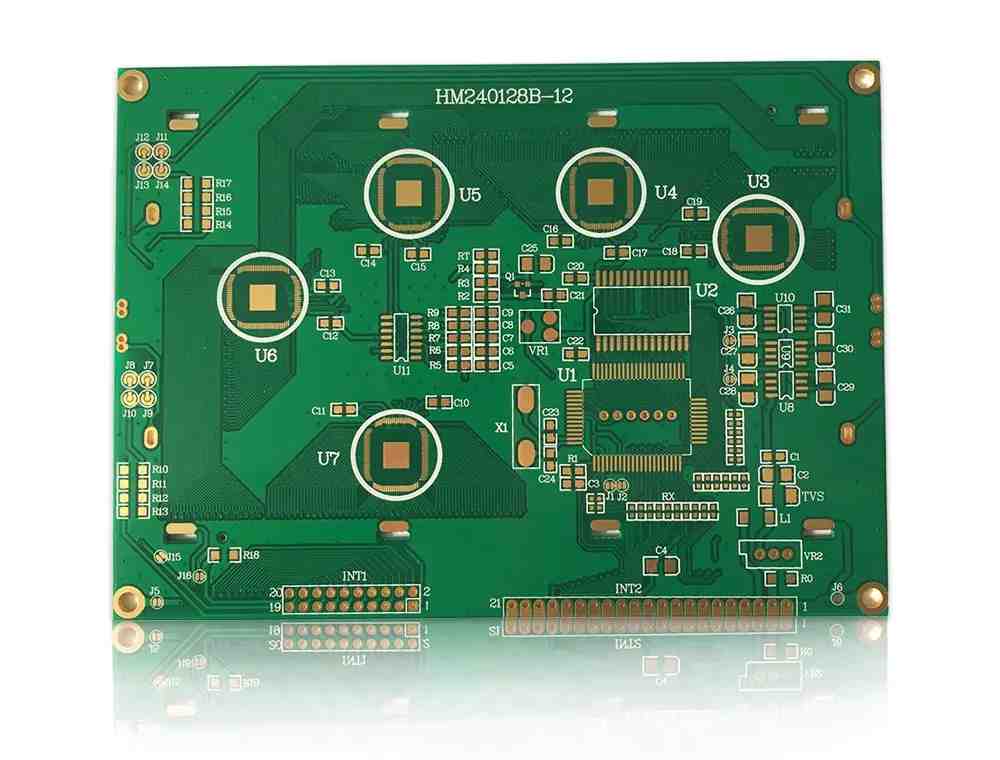

信號分組:

DDR2 BUS信號通常被布線成幾組,同一組的信號具有相關或相似的信號特性。

時鐘組:差分時鐘信號,每對信號的頻率和相位相同。 ck0p 和 ck0n 是一對。

數據組:對于64位DDR2主板內存,每8位(即一個字節)數據可分為八組,包括數據dq[0:7]、數據掩碼dqm0、數據門控差分信號dqsp0和dqsn0 , 等等。 同一數據組的信號應走在同一層,且層數也應一起改變。 VIA 的數量應該相同。 數據位可以互換,以便于同一信號層中的布線。 比如dq2信號走線時,發現如果按照原理圖走線,會和dq4信號錯開。 這樣,我們就必須換層來路由信號。 我們可以通過交換數據位來使信號走同一層。 對于內存來說,每一位存儲的就是讀取的內容。 交換不會受到影響,但交換條件必須在同一組的八個位之間。

地址/命令組:MA [0:14]、BA0、BA1、BA2、RAS、CAS、WE。

控制組:時鐘使能CKE、片選CS、終端電阻門ODT為一組。 對于內存模塊,DIMM0 使用 CKE0、CKE1、CS0、CS1、ODT0 和 ODT1。 在設計板載存儲器時,只能使用CKE0、CS0和ODT0來控制4個16位存儲器芯片。

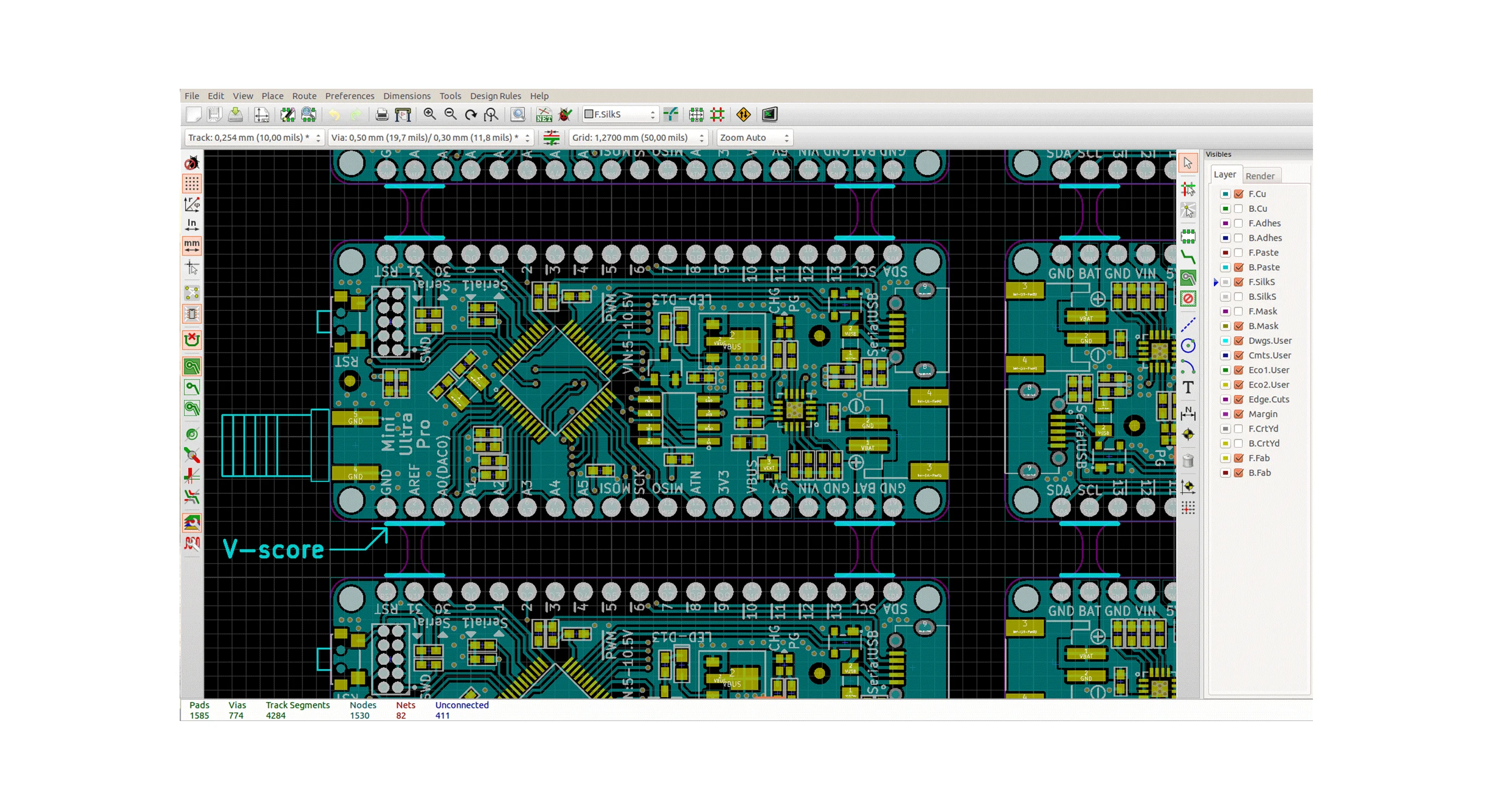

PCB 堆疊:

對于六層板,一般疊片為頂部、GND、singnal2、singnal3、POWER 和底部。 一般情況下,以GND作為信號的參考面比較好。 走線的阻抗由走線寬度、走線銅箔厚度、走線到參考平面的距離、參考平面銅箔厚度以及板介質材料決定。 設計PCB時,應根據CPU制造商的阻抗設計要求來設置堆疊。 一般的PCB設計軟件也可以計算阻抗。 找到PCB廠家了解板介質的厚度信息,然后就可以自己設計疊層和線寬了。 地址/命令信號和控制信號可以以1.8V存儲器工作電壓為參考平面。 但是,必須參考完整的電源層。

布線長度控制:

對于DDR2這樣的高頻信號,需要計算到CPU核心的走線長度,這就引入了一個叫做封裝長度的概念。 通過物理、化學的方法將硅片蝕刻成CPU核心,然后將CPU核心封裝到一塊小小的PCB基板上就是我們常見的CPU。 小PCB上的引腳到CPU核心的走線長度稱為封裝長度,也稱為PIN延遲。

同級別內存的時鐘長度應控制在正負5mil以內。

同一數據組中所有導線的長度應控制在數據選通信號DQS的正負20密耳之內。 不同數據組之間的長度可以不同,但應控制在時鐘信號的正負 500 mil 范圍內。

地址/命令組信號的長度沒有嚴格控制,要求INTEL霧化N450控制在時鐘信號的負500mil到正1000mil范圍內。 也就是說最長的信號和最短的信號可以相差1500mil,但是布線時最好減小信號長度的差異。 布線時,這組信號的長度完全相等是沒有問題的,但也占用了大量的PCB空間和時間。 如果地址/命令信號長度超過時鐘信號數千mil,則需要在BIOS固件中進行適當調整。 應控制在CPU要求的范圍內。 當需要做板載內存時,只需配置內存SPD即可。

控制組信號長度的控制要求與地址/命令組信號類似。 應根據CPU制造商的要求進行設計。 INTEL Agitation N450 要求控制在0 mil 到+1000 0mil 的時鐘信號范圍內。

線距:

一般來說,走線應遵循3W原則,即同一水平線與走線之間的距離為走線寬度的3倍。 然而,這不是必要的。 Intel的要求相對較小。 一般來說,繞組線之間的間距可以是16到20mil,時鐘信號可以增加到30mil。 不同組信號之間的距離應適當延長,可大于20mil,地址/命令組與控制組信號之間的距離可小于8mil。 BGA扇出之間的距離可以很小,出線應根據CPU設計要求進行布線。

其他電源路由:

VREF接線可以使用20mil的電線,并且每個連接的設備都要加一個0.1uf的電容。

VTT接線應大于135mil。 每四個電阻接一個0.1uf的電容,兩端接一個10uf的大電容。

點對多點信號,如地址/命令信號、控制信號、時鐘信號等應走“T”形,即芯片向上,中間分支,長度滿足CPU 設計要求。 PCB組裝及PCB加工廠家講解DDR2 PCB布局經驗總結、信號分組、數據分組、堆棧結構。

然后

聯系

電話熱線

13410863085Q Q

微信

- 郵箱