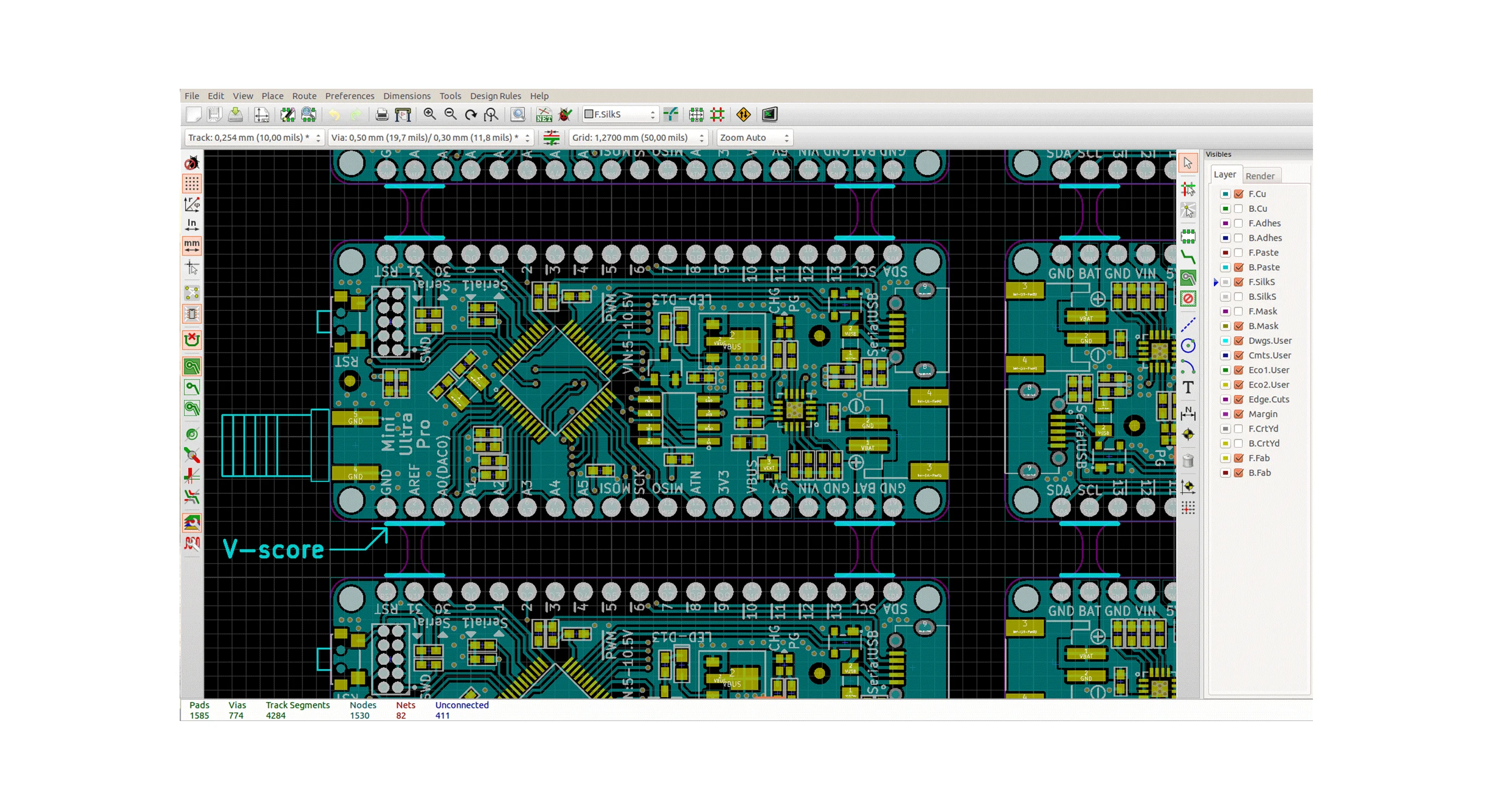

PCB電路板設(shè)計(jì),解釋電路板設(shè)計(jì)并繪制了一些平行線

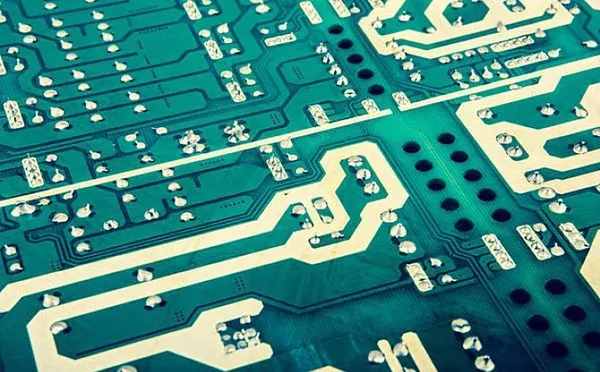

印刷電路板的性能還應(yīng)考慮便利性。 額外的路由長(zhǎng)度是有損的。 此外,信號(hào)在較長(zhǎng)的路線上也會(huì)衰減,因?yàn)橛懈嗟墓裘娌⑶以肼暟l(fā)生器可以耦合到信號(hào)。 我們必須在可用的幾何形狀內(nèi)工作,這給我們留下了無(wú)數(shù)的選擇。

氣隙和銅厚是相互關(guān)聯(lián)的。

這讓我想起了我們?cè)谠O(shè)計(jì) PCB 時(shí)必須考慮的其他妥協(xié)。 首先,大電流的電路板將受益于厚銅層來(lái)處理電源。 同時(shí),我們也喜歡使用較窄的走線,將它們封裝在一起,以避免較大設(shè)備的內(nèi)部面積。

讓正確的堆棧達(dá)到平衡作用可以實(shí)現(xiàn)一些細(xì)間距連接以及一些高電流應(yīng)用。 該設(shè)置的設(shè)計(jì)規(guī)則將允許信號(hào)層上有更小的氣隙,而其他規(guī)則則設(shè)置更寬的上電間隔規(guī)則。

這兩個(gè)東西不可能是好鄰居,所以我們需要其他層面來(lái)充當(dāng)障礙。 添加層數(shù)會(huì)增加成本,所以我們必須充分利用可用的層數(shù)。 在某些情況下,小間距規(guī)則僅適用于局部區(qū)域。 一旦沒(méi)有連接器或處理器,就會(huì)應(yīng)用一組更保守的規(guī)則。 在這個(gè)過(guò)程中撥號(hào)是一種平衡行為。

元件如何放置?

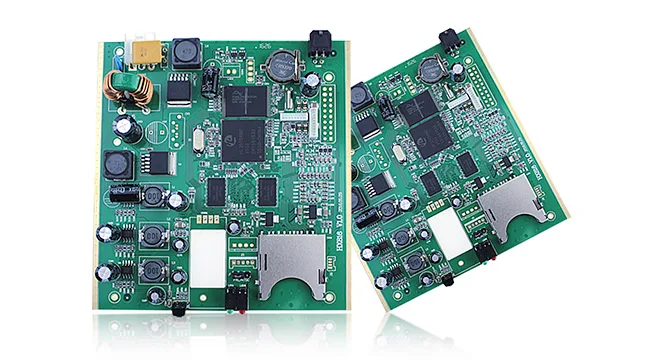

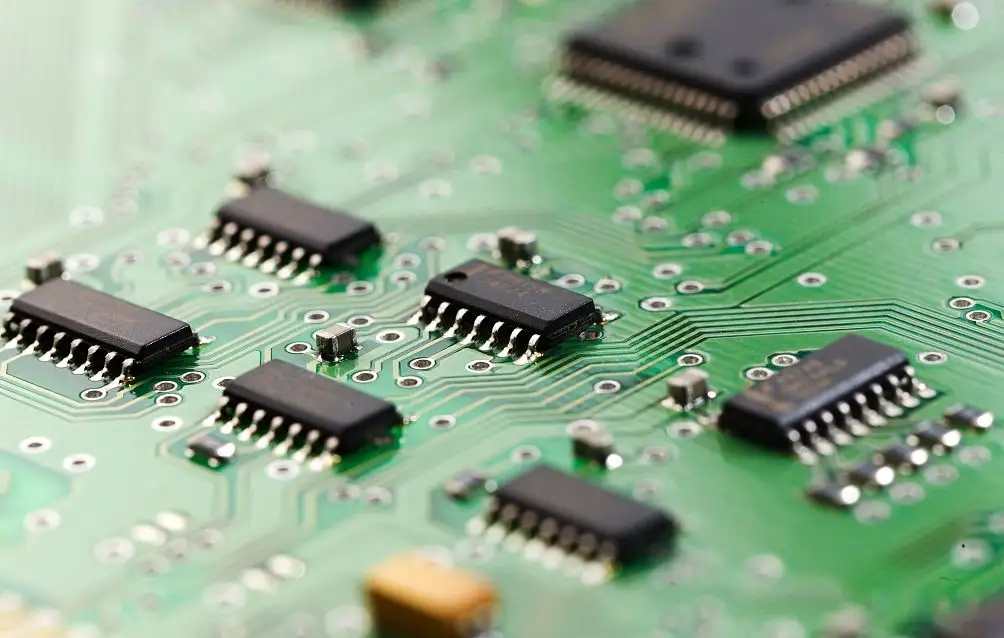

我們知道小尺寸是首選。 這就是那些高度集成電路的來(lái)源。 “通用”片上系統(tǒng) (SOC) 實(shí)際上將擁有數(shù)百個(gè)無(wú)源元件,或許還有數(shù)十個(gè)其他集成電路來(lái)實(shí)際創(chuàng)建一個(gè)系統(tǒng)。 大多數(shù)這些附加電路都希望盡可能靠近 SOC。

所有內(nèi)存和高速鏈路都想在談判桌上占據(jù)一席之地。 可能需要足夠的功率來(lái)確保使用短的特殊電源管理IC或PMIC。 當(dāng)然,任何模擬線都應(yīng)該短而直,并且不應(yīng)該超出SOC的范圍。 為什么這些功能一開(kāi)始不在SOC上?

這歸結(jié)于芯片架構(gòu)。 與構(gòu)成大部分 SOC 空間的幾乎看不見(jiàn)的晶體管柵極相比,存儲(chǔ)單元非常大。 這些東西一定要放在自己的包裝里,只是因?yàn)樗麄兪窃O(shè)計(jì)的制造商。

然而,計(jì)算設(shè)備周圍的區(qū)域是熱門商品。 我的意思是字面意思。 周圍放置的空間越多越好。 面對(duì)小尺寸的要求,這樣的文件。 我們希望各個(gè)部分彼此靠近,同時(shí)又分開(kāi)。

所有這些競(jìng)爭(zhēng)因素將導(dǎo)致戰(zhàn)略集群,通常通過(guò)其對(duì)事物的電壓分解,而次要焦點(diǎn)是其路由。 在PCB組裝放置的平衡過(guò)程中,我們還考慮了熱干擾和電磁干擾。 如果能夠進(jìn)一步擴(kuò)展內(nèi)容,就可以增加測(cè)試的訪問(wèn)權(quán)限。 同時(shí),如果我們能夠壓縮整個(gè)電路板,以便在比去年的產(chǎn)品更小的外殼中為更大的電池騰出空間,那就太好了。

印刷電路板接線時(shí)的權(quán)衡

因此,布線是布局的函數(shù),而布局是如上所述的幾個(gè)因素的函數(shù)。 其中一些因素相互直接競(jìng)爭(zhēng)。 即使有最好的模擬,也很難預(yù)測(cè)重疊的細(xì)微差別。 完美是遙不可及的,所以我們所追求的就足夠了。 如果在保修期內(nèi)運(yùn)行可靠,我們的工作就完成了。

給定足夠長(zhǎng)度的跑道,理論上我們可以使用完美的內(nèi)存總線,它使用最小的曲折和最小的空間,同時(shí)保持各種連接的最佳間距。 時(shí)間預(yù)算可以設(shè)置為最小允許偏差。 問(wèn)題是時(shí)間幾乎總是很短,因此我們需要信號(hào)可以處理的所有范圍。

讓每個(gè)人都高興似乎是不可能的。 每個(gè)人,不僅包括內(nèi)部團(tuán)隊(duì),還包括每個(gè)供應(yīng)商,都提供了圍繞他們的芯片構(gòu)建的參考設(shè)計(jì),就好像它將成為板上唯一的東西一樣。 電路板組裝和電路板加工廠家解釋電路板設(shè)計(jì)并畫(huà)一些平行線。 在性能方面,還應(yīng)考慮便利性。 額外的布線長(zhǎng)度被浪費(fèi)了。

然后

聯(lián)系

電話熱線

13410863085Q Q

微信

- 郵箱