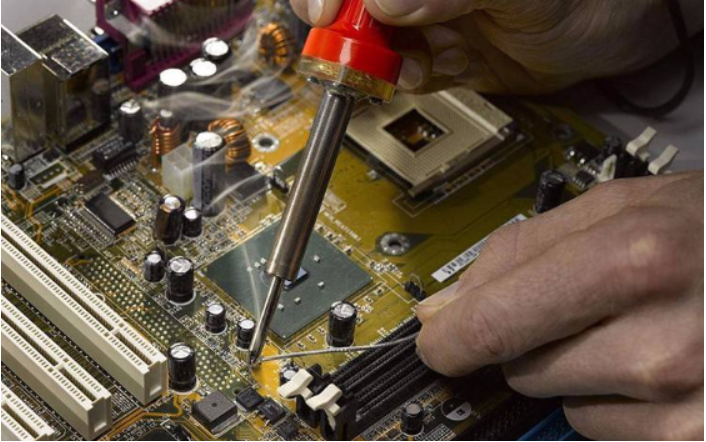

PCB工藝降低噪聲和電磁干擾的經驗

1、串聯電阻可以用來降低控制電路上下沿的跳變率。

2、盡量使時鐘信號電路周圍電位接近于零,時鐘區用地線繞一圈。 時鐘線應盡可能短。

3、I/O驅動電路盡量靠近印制板邊緣。

4、不用的門電路輸出端不要懸空。 不用的運放正輸入端接地,負輸入端接輸出端。

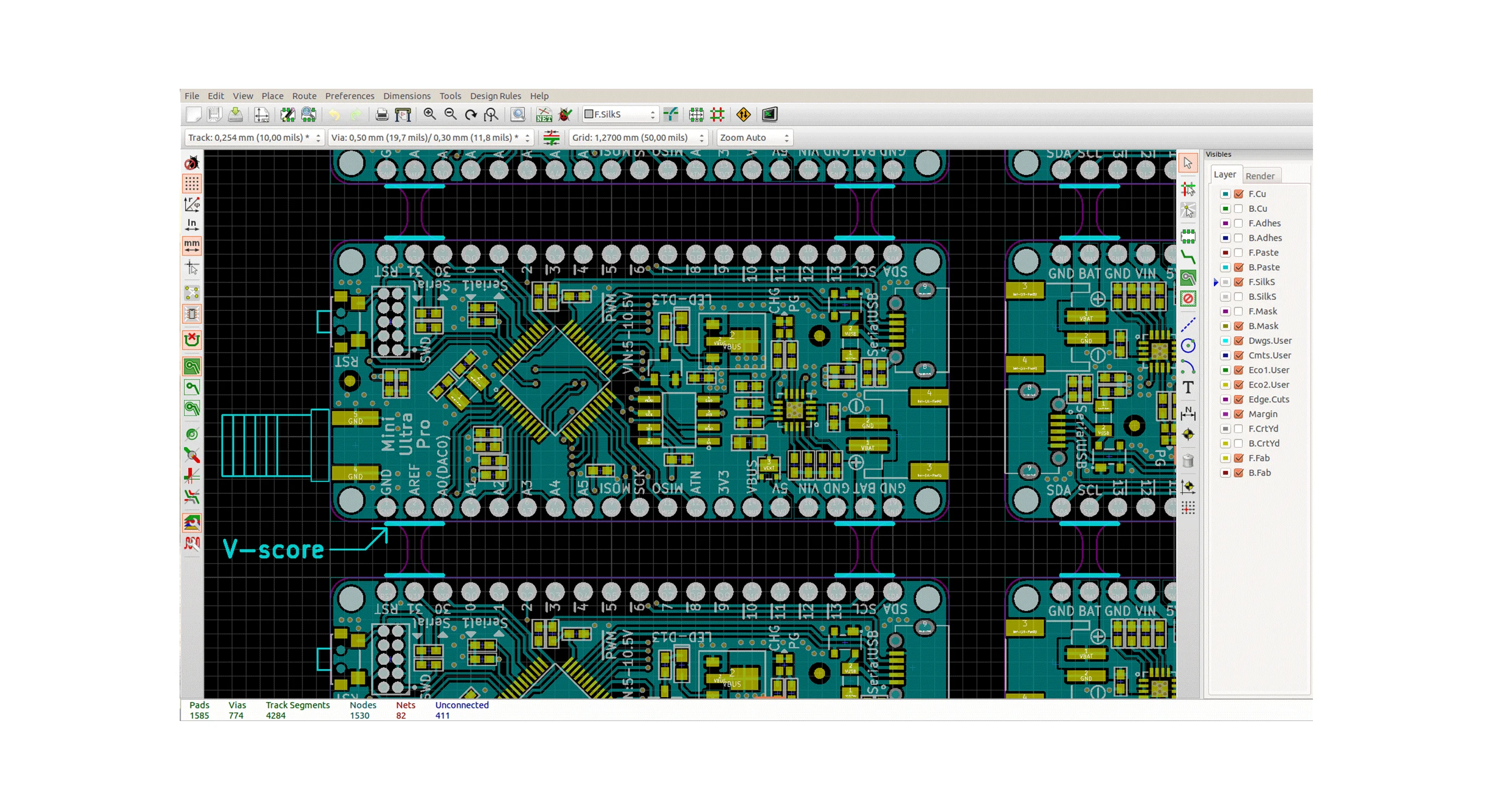

5、盡量用45°折線代替90°折線,減少高頻信號對外傳輸和耦合。

6、垂直于I/O線的時鐘線比平行于I/O線的時鐘線干擾小。

7、PCB元器件的引腳盡量短。

8、不要在石英晶振或對噪聲特別敏感的元器件下面走線。

9、弱信號電路和低頻電路周圍的地線不得形成電流環路。

10、必要時在線路上加鐵氧體高頻扼流圈,隔離信號、噪聲、電源和地。

PCB 上的一個通孔會產生大約 0.6pF 的電容; 集成電路本身的封裝材料造成2pF~10pF的分布電容; 電路板上的連接器,520μH的分布電感; 雙列直插式24腳集成電路插座,引入4μH~18μH的分布電感。

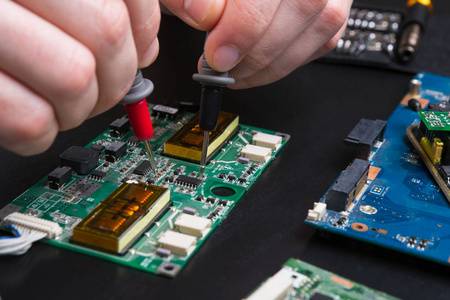

數字電路與單片機的抗干擾設計

在PCB電子系統設計中,為減少走彎路、節省時間,應充分考慮并滿足抗干擾要求,避免在設計完成后采取抗干擾補救措施。 形成干擾的三個基本要素:

(1) 干擾源是指產生干擾的元件、設備或信號,用數學語言表示為:du/dt、di/dt

方是干擾源。 例如雷電、繼電器、可控硅、電機、高頻時鐘等都可能成為干擾源。

(2)傳播路徑是指干擾從干擾源傳播到敏感器件所經過的路徑或介質。 典型的干擾傳播路徑是通過導體傳導和空間輻射。

(3) 敏感設備是指容易被干擾的對象。 例如:A/D、D/A轉換器、單片機、數字IC、弱信號放大等等。

PCB抗干擾設計的基本原則是抑制干擾源,切斷干擾傳播路徑,提高敏感器件的抗干擾性能。

抑制干擾源

抑制干擾源就是盡可能降低干擾源的du/dt、di/dt。 這是PCB抗干擾設計中最優先、最重要的原則,往往能達到事半功倍的效果。 主要通過在干擾源兩端并聯電容來降低干擾源的du/dt。 通過在干擾源電路中串聯電感或電阻和續流二極管來降低干擾源的di/dt。

抑制干擾源的常用措施如下:

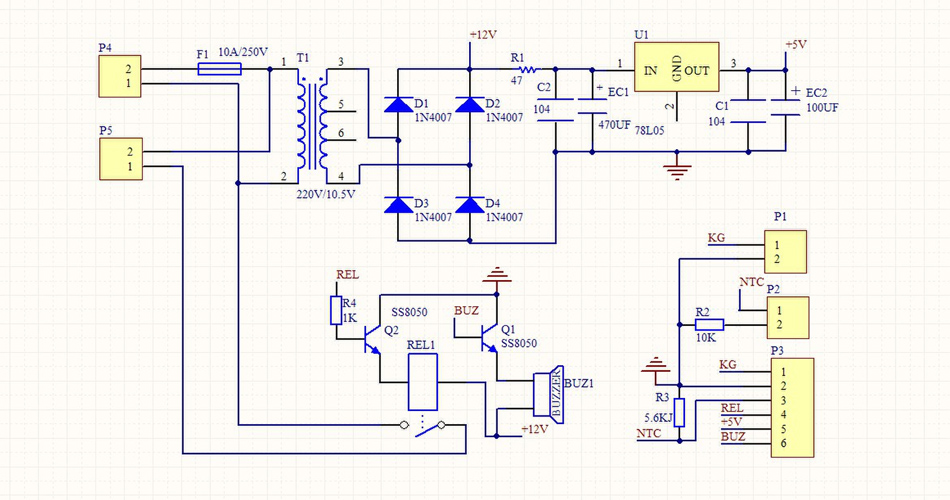

(1)繼電器線圈加裝續流二極管,消除線圈斷開時產生的反電動勢干擾。 只加續流二極管會延遲繼電器的斷開時間,加穩壓二極管后繼電器在單位時間內可以動作更多次。

(2)繼電器觸點兩端并聯火花抑制PCB電路(一般為RC串聯電路,電阻一般選用K~幾十K,電容選用0.01uF),以減少電火花的影響。

(3)在電機上加濾波電路,注意電容和電感引線盡量短。

(4) PCB上每顆IC應并聯0.01μF~0.1μF的高頻電容,以減小IC對電源的影響。 注意高頻電容的接線。 接線應靠近電源端子,并盡可能短。 否則會增大電容的等效串聯電阻,影響濾波效果。

(5)PCB布線時避免90度折線,以減少高頻噪聲發射。

(6)在晶閘管兩端并聯RC抑制電路,以降低晶閘管產生的噪聲(噪聲嚴重時,晶閘管可能被擊穿)。

根據干擾的傳播路徑,可分為傳導干擾和輻射干擾

所謂傳導干擾是指通過導線傳遞給敏感器件的干擾。 高頻干擾噪聲的頻帶與有用信號的頻帶不同。 可以通過在導線上加一個濾波器來切斷高頻干擾噪聲的傳輸。 有時,可以加入隔離光耦來解決這個問題。 電源噪聲危害最大,處理時應特別注意。 所謂輻射干擾是指通過空間輻射傳遞給敏感設備的干擾。 一般的解決辦法是增加干擾源與敏感器件的距離,用地線隔離,在敏感器件上加屏蔽。

本文介紹PCB工藝中降低噪聲和電磁的PCB抗干擾設計經驗

然后

聯系

電話熱線

13410863085Q Q

微信

- 郵箱