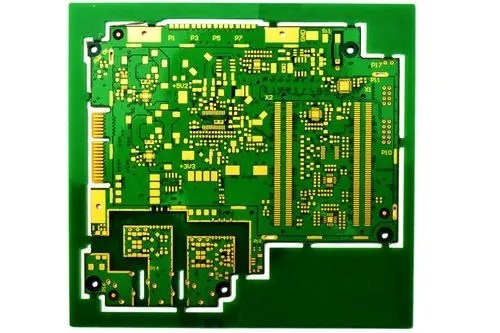

高速高密度PCB設(shè)計、電源完整性的新挑戰(zhàn)

面對高速、高密度PCB設(shè)計的挑戰(zhàn),設(shè)計人員需要改變的不僅是工具,還有設(shè)計方法、理念和流程。

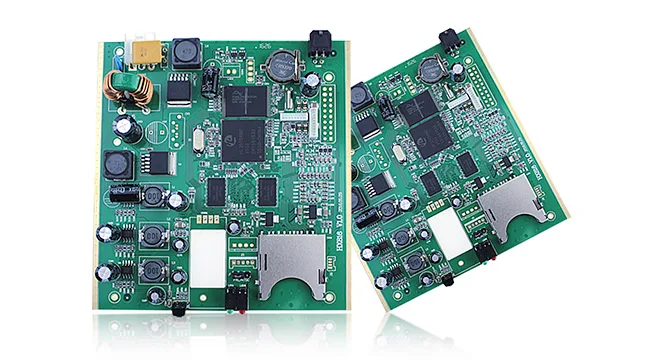

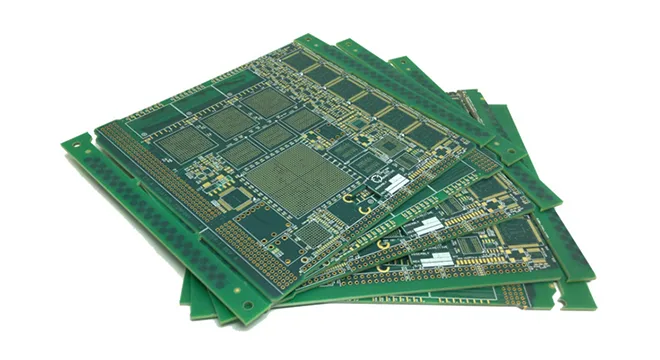

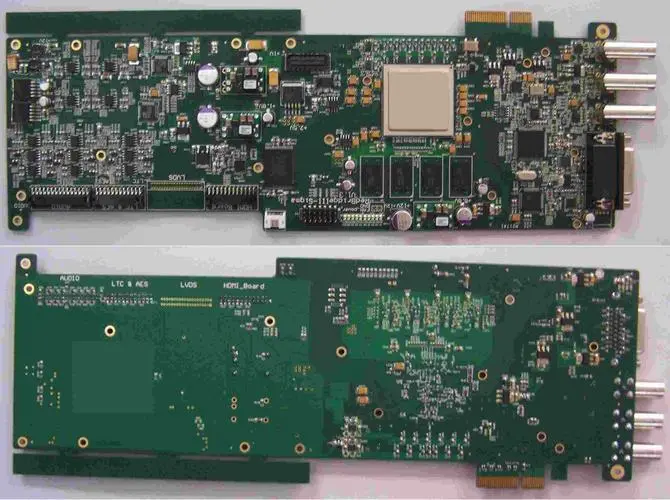

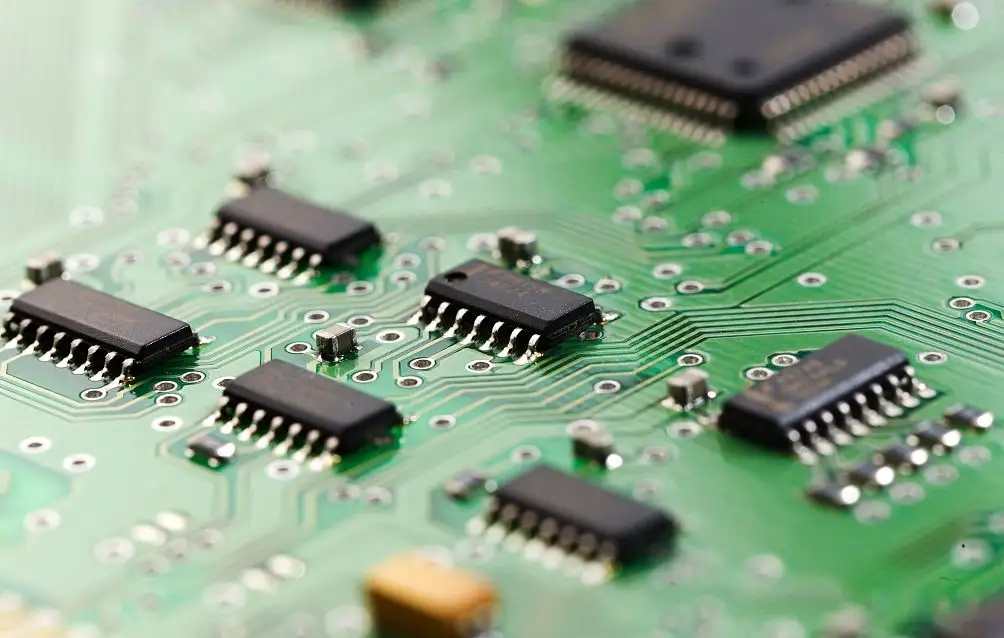

隨著電子產(chǎn)品功能的日益復(fù)雜和性能的提高,印刷電路板的密度及其相關(guān)元件的頻率不斷提高,工程師面臨著高速、高密度PCB設(shè)計帶來的挑戰(zhàn) 也在增加。

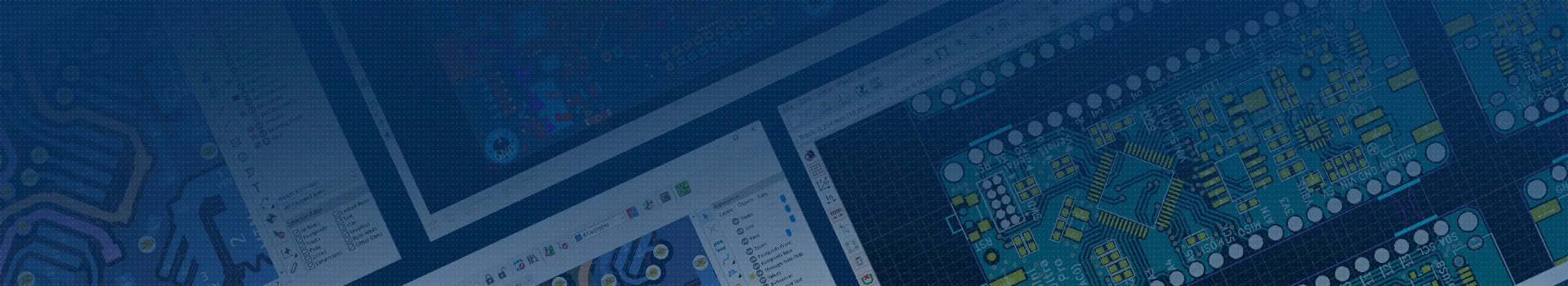

隨著競爭的加劇,制造商在產(chǎn)品上市時間上面臨著越來越大的壓力。 如何利用先進(jìn)的EDA工具和優(yōu)化方法和流程,高質(zhì)量、高效率地完成設(shè)計,成為系統(tǒng)制造商和設(shè)計工程師不得不面對的問題。

熱點:從信號完整性轉(zhuǎn)向電源完整性

說到高速設(shè)計,人們首先想到的是信號完整性。 信號完整性主要是指信號線上信號傳輸?shù)馁|(zhì)量。 當(dāng)電路中的信號能夠按要求的時序、持續(xù)時間和電壓幅度到達(dá)接收芯片引腳時,電路具有良好的信號完整性。 當(dāng)信號無法正常響應(yīng)或信號質(zhì)量無法使系統(tǒng)長期穩(wěn)定工作時,就會出現(xiàn)信號完整性問題。 信號完整性主要表現(xiàn)在延遲、反射、串?dāng)_、定時、振蕩等方面。 一般認(rèn)為,當(dāng)系統(tǒng)工作在50MHz時,會出現(xiàn)信號完整性問題。 隨著系統(tǒng)和設(shè)備頻率的不斷增加,信號完整性問題將變得更加突出。 元器件和PCB板的參數(shù)、PCB板上元器件的布局、高速信號的布線等問題都會造成信號完整性問題,導(dǎo)致系統(tǒng)運行不穩(wěn)定,甚至徹底失效。

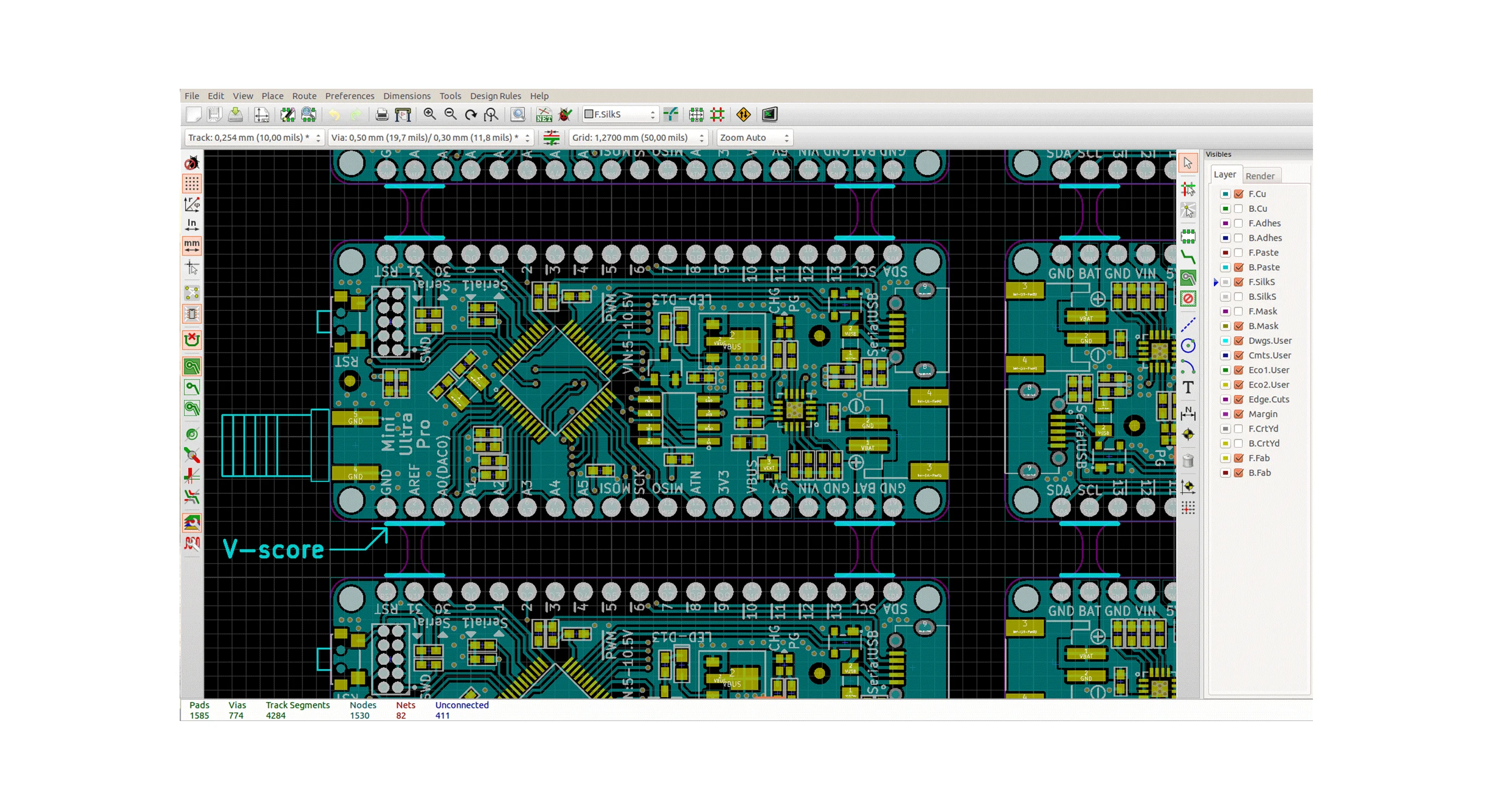

經(jīng)過幾十年的發(fā)展,信號完整性技術(shù)的理論和分析方法已經(jīng)比較成熟。 至于信號完整性,陳蘭冰認(rèn)為,信號完整性不是某人的問題。 它涉及到設(shè)計鏈的每一個環(huán)節(jié)。 不僅系統(tǒng)設(shè)計工程師、硬件工程師、PCB工程師要考慮,在制造中也不能忽視。 解決信號完整性問題必須使用先進(jìn)的仿真工具,比如CADence的SPECTRAQuest,可以在設(shè)計前期進(jìn)行建模和仿真,從而形成約束規(guī)則來指導(dǎo)后期的布局布線 并提高設(shè)計效率。 隨著今年6月Cadence針對千兆赫信號的仿真器MGH的推出,這是業(yè)界首款能夠在幾秒內(nèi)完成數(shù)萬BIT千兆赫信號的仿真器,信號完整性技術(shù)得到了提升。

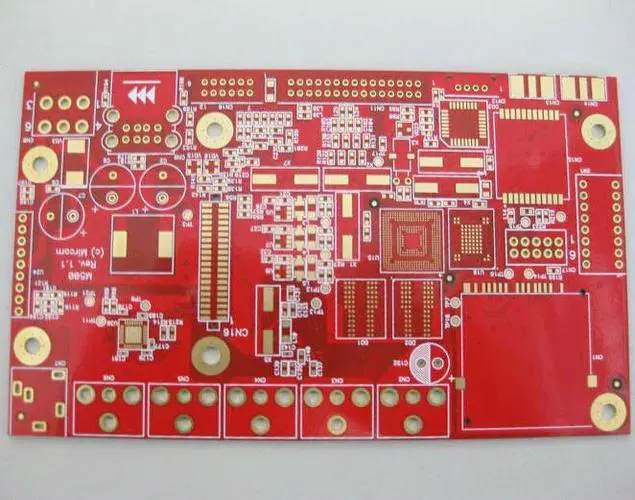

與信號完整性相比,電源完整性是一項相對較新的技術(shù),被認(rèn)為是高速高密度PCB設(shè)計中最大的挑戰(zhàn)之一。 電源完整性是指在高速系統(tǒng)中,PDS供電系統(tǒng)在不同頻率下具有不同的阻抗特性,使得電路板上各處的電源層與PCB上的地層之間的電壓不同,導(dǎo)致電源不連續(xù)。 電源、電源噪聲、芯片無法正常工作; 同時,由于高頻輻射,電源完整性問題也會帶來EMC/EMI問題。 如果電源完整性問題不能得到很好的解決,將會嚴(yán)重影響系統(tǒng)的正常運行。

一般來說,電源完整性問題可以通過兩種方式解決:優(yōu)化電路板的堆疊設(shè)計和布局,以及增加去耦電容。 當(dāng)系統(tǒng)頻率小于300~400MHz時,去耦電容可以抑制頻率、濾波和阻抗控制。 在適當(dāng)?shù)奈恢梅胖煤线m的去耦電容可以幫助減少系統(tǒng)電源完整性的問題。 但當(dāng)系統(tǒng)頻率較高時,去耦電容作用不大。 在這種情況下,只能通過優(yōu)化電路板的層間距設(shè)計、布局布線或其他方法來降低電源和地噪聲(如適當(dāng)匹配以減少電源傳輸?shù)姆瓷鋯栴})來解決電源完整性問題。 系統(tǒng)),同時抑制 EMC/EMI。

對于信號完整性和功率完整性的關(guān)系,陳蘭冰認(rèn)為:“信號完整性是時域的概念,比較容易理解,而功率完整性是頻域的概念,比信號完整性更難理解,但 電源完整性在某些方面與信號完整性有相似之處,電源完整性對工程師的技能要求較高,對高速設(shè)計來說是一個新的挑戰(zhàn),不僅涉及板級,還涉及芯片級和封裝級,建議從事高速設(shè)計的工程師 高速電路板設(shè)計應(yīng)以信號完整性的解決方案為基礎(chǔ)來解決電源的完整性。”據(jù)悉,Cadence的電源完整性工具PI已推向市場,并已成功應(yīng)用于多家客戶的設(shè)計中。

然后

聯(lián)系

電話熱線

13410863085Q Q

微信

- 郵箱