PCB 布局上的串擾可能會造成災難性后果。 如果不加以糾正,串擾可能會導致成品電路板根本無法工作或時斷時續地出現問題。 下面我們就來看看什么是串擾,以及在高速PCB設計中如何防止串擾。

什么是高速PCB設計中的串擾?

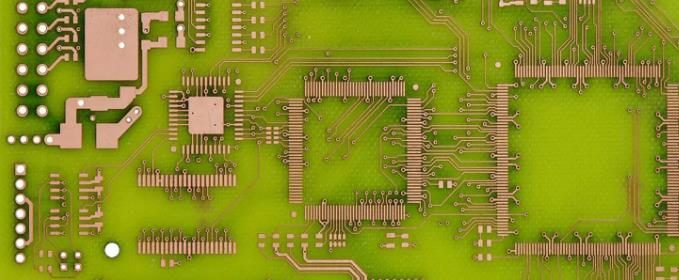

串擾是在 PCB 上運行的導線之間意外的電磁耦合。 這種耦合可能會導致一條跡線的信號脈沖無法作用于另一條跡線的信號,即使它們實際上并未相互接觸。 當平行運行之間的距離非常窄時,可能會發生這種情況。 盡管跡線可能會出于制造目的而保持最小間距,但它們可能不足以滿足電磁目的。

考慮兩條路線彼此平行。 如果一條跡線中的信號幅度大于另一條跡線,則可能會嚴重影響另一條跡線。 然后,“受害者”跡線中的信號將開始模仿攻擊者跡線的特性阻抗,而不是傳輸自己的信號。 發生這種情況時,就會遇到串擾。

一般認為串擾發生在同一層上相鄰的兩條平行線路之間。 然而,相鄰層上的兩條相鄰平行線路之間可能會發生串擾。 這稱為寬邊耦合,因為相鄰兩個信號層之間的核心厚度很小,因此更容易發生這種情況。 該厚度可以是 4 密耳(0.1 毫米),有時小于同一層上兩次運行之間的距離。

消除高速設計中的潛在串擾

幸運的是,您不會受到串擾的影響。 您可以通過專注于最小化串擾的高速 PCB 設計來避免這些問題。 以下是一些可以幫助您消除板上串擾可能性的高速設計技術:

差分對與其他信號路徑之間的距離應盡可能大。 經驗法則是間隙 = 走線寬度的 3 倍。

時鐘走線與其他信號走線之間的差異應盡可能大。 同樣的gap=3倍拇指寬度規則也適用于此。

保持不同差分對之間的距離盡可能大。 這里的經驗法則是稍微大一點,gap=5倍走線寬度。

異步信號(如RESET、INTERRUPT等)要遠離總線和高速信號。 然而,由于這些信號在電路板的正常操作中很少使用,因此可以將它們路由到開、關或開機信號旁邊。

確保板疊中相鄰的兩個信號層會交替改變水平和垂直布線方向。 通過不允許路由線彼此平行延伸,將減少寬邊耦合的機會。

減少兩個相鄰信號層之間潛在串擾的更好方法是在微帶配置中將它們之間的層與接地層分開。 地平面不僅會增加兩個信號層之間的距離,還會為信號層提供所需的返回路徑。

設計軟件如何幫助您消除高速PCB設計中的串擾

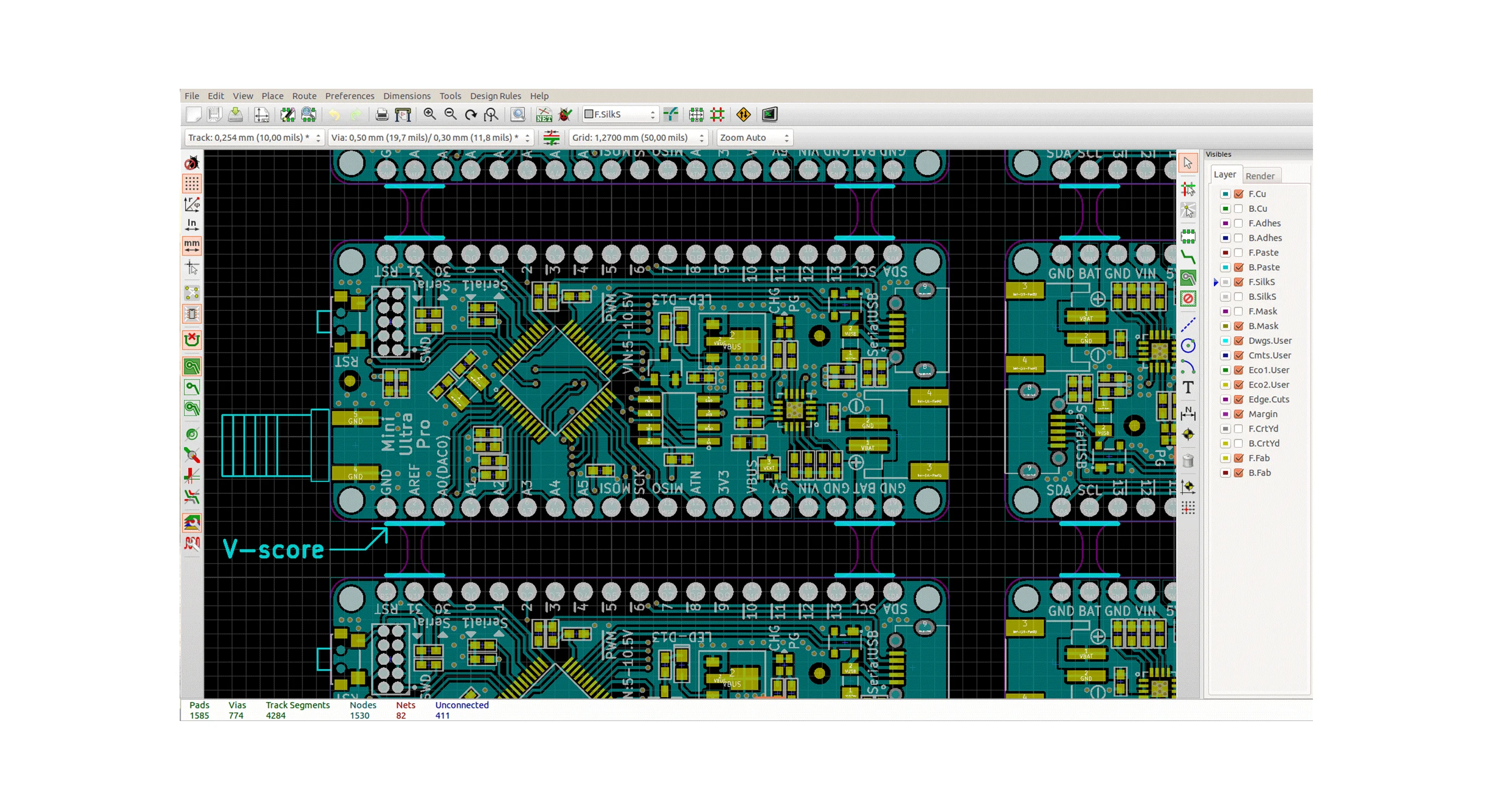

PCB 設計工具具有許多內置功能,可幫助您避免設計中的串擾。 電路板層規則將通過指定布線方向和創建微帶堆棧來幫助您避免寬邊耦合。 使用網絡類別規則,您將能夠為更容易受到串擾影響的網絡組分配更大的路由間隔。 差分對路由器會將差分對作為實際對一起布線,而不是單獨布線。 這樣,可以保持差分對路由線路與其他網絡之間所需的間距,以避免串擾。

除了高速PCB設計軟件的內置功能外,還有其他工具也可以幫助您消除高速PCB設計中的串擾。 有不同的串擾計算器可幫助您確定正確的布線寬度和布線間距。 還有一個信號完整性模擬器,可以分析您的高速設計中是否存在潛在的串擾問題。

如果允許串擾,則可能是印制電路板上的大問題。 既然您知道要尋找什么,就可以準備防止串擾了。 我們在此討論的設計技術和高速 PCB 設計軟件的功能將幫助您創建無串擾設計。 PCB加工廠講解:什么是高速PCB設計中的串擾? 如何消除串擾和潛在的串擾?

然后

聯系

電話熱線

13410863085Q Q

微信

- 郵箱