嵌入式系統如何提高PCB信號的完整性

隨著電子技術的不斷進步,嵌入式系統將應用到越來越多的領域。 在這眾多的應用中,人們考慮的不再是功能和性能,而是可靠性和兼容性。 那么,如何通過布線技術提高嵌入式系統PCB的信號完整性就成了一個“重要課題”。

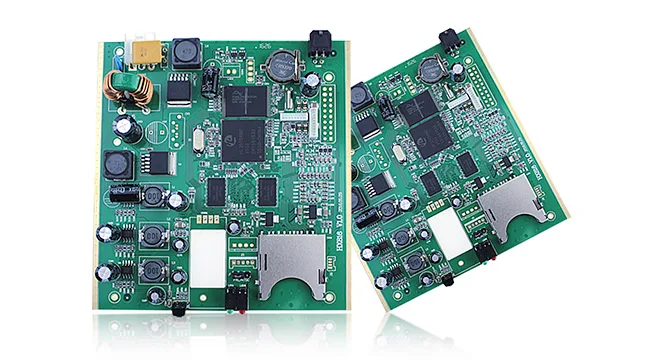

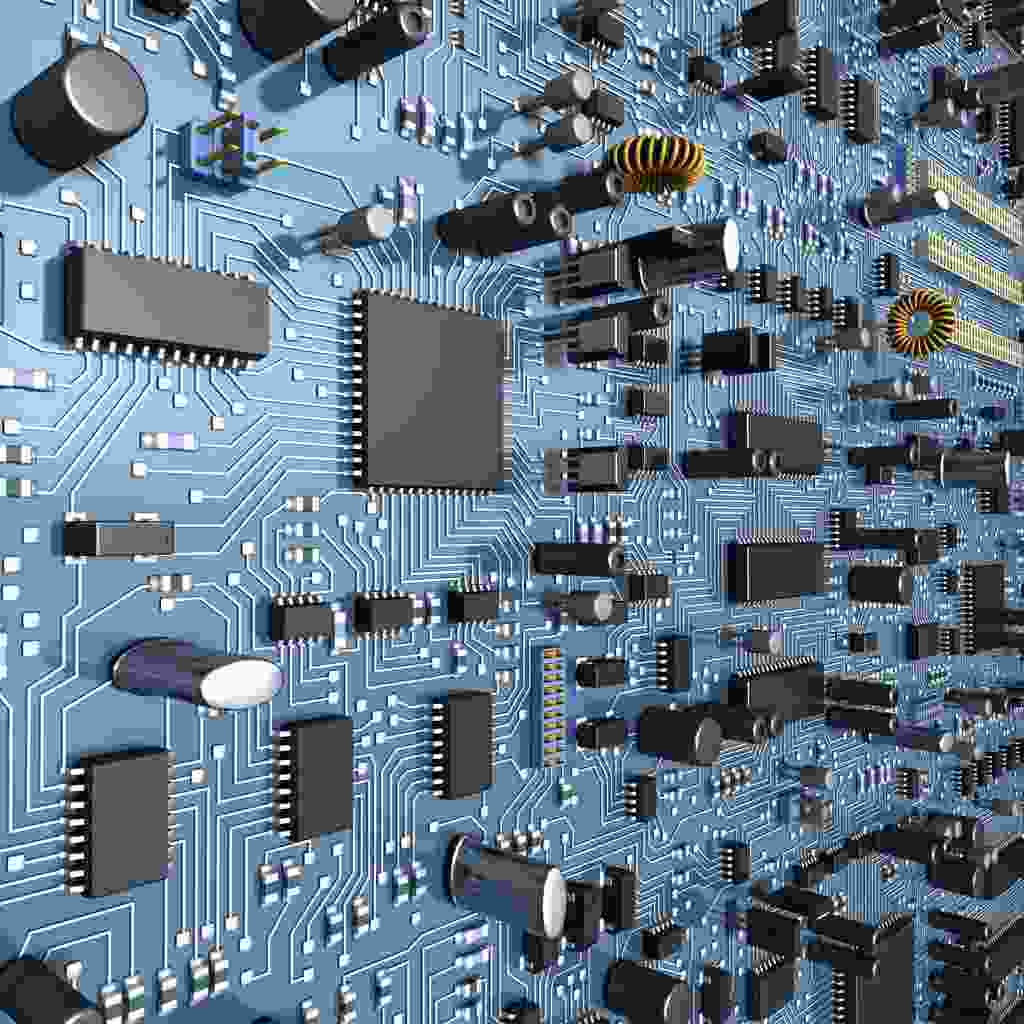

眾所周知,PCB(印刷電路板)是電子產品中電路元器件的基本支撐,其設計質量往往直接影響嵌入式系統的可靠性和兼容性。 以往,在一些低速電路板中,時鐘頻率一般只有10MHz左右。 電路板或封裝設計的主要挑戰是如何在雙層板上布線所有信號線,以及如何在組裝過程中不損壞封裝。

互連的電氣特性并不重要,因為它們不會影響系統性能。 從這個意義上講,低速信號電路板中的互連是平滑和透明的。 但隨著嵌入式系統的發展,所用的電路基本都是高頻電路。 隨著時鐘頻率的增加,信號的上升沿也變短。 印制電路對通過信號的容抗和感抗會遠大于印制電路本身的電阻,嚴重影響信號的完整性。 對于嵌入式系統,當時鐘頻率超過100MHz或上升沿小于1ns時,信號完整性的影響就變得很重要。

在PCB中,信號線是信號傳輸的主要載體。 信號線的走線將直接決定信號傳輸的優劣,從而直接影響到整個嵌入式系統的性能。 布線不合理會嚴重引起各種信號完整性問題,對電路產生時序、噪聲和電磁干擾(EMI),嚴重影響嵌入式性能。 本文從高速數字電路中信號線的實際電氣特性出發,建立電氣特性模型,找出影響信號完整性的主要原因和解決問題的方法,以及應解決的問題。 并給出了接線時應遵循的方法和技巧。

信號完整性

信號完整性是指信號線上信號的質量,即信號在電路中以正確的時序和電壓電平響應的能力。 具有良好信號完整性的信號是指在需要時具有所需的電壓電平值。 信號完整性差不是單一因素造成的,而是板級設計中的多種因素造成的。 信號完整性問題體現在很多方面,主要有延遲、反射、串擾、過沖、振蕩、地球炸彈等。

延時:延時是指信號在PCB板的傳輸線上以有限的速度傳輸,信號從發送端到接收端,其間存在傳輸延遲。 信號延遲會影響嵌入式時序; 傳輸延遲主要取決于導線的長度和導線周圍介質的介電常數。 在高速數字系統中,信號傳輸線的長度是影響時鐘脈沖相位差最直接的因素。 時鐘脈沖相位差是指同時產生的兩個時鐘信號不同步到達接收端。 時鐘脈沖的相位差降低了信號到達的可預測性。 如果時鐘脈沖的相位差太大,接收端就會產生錯誤信號。

反射:反射是信號在信號線上的回波。 當信號延遲時間遠大于信號跳躍時間時,必須將信號線視為傳輸線。 當傳輸線的特性阻抗與負載阻抗不匹配時,信號功率(電壓或電流)的一部分傳輸到線路并到達負載,但也有一部分被反射。 如果負載阻抗小于原阻抗,則反射為負; 相反,反思是積極的。 布線幾何形狀的變化、不正確的接線端接、通過連接器的傳輸以及電源層的不連續性都會導致此類反射。

串擾:串擾是指由于兩條信號線之間的耦合、信號線之間的互感和互容而引起的信號線上的噪聲。 電容耦合導致耦合電流,而電感耦合導致耦合電壓。 串擾噪聲源于信號線之間、信號系統與配電系統之間以及過孔之間的電磁耦合。 串行繞組可能會造成時鐘錯誤、間歇性數據錯誤等,影響相鄰信號的傳輸質量。 現實中,串擾無法完全消除,但可以控制在系統能夠承受的范圍內。 PCB層數參數、信號線間距、驅動器和接收器的電氣特性、基線端接方式等對串擾有一定的影響。

過沖和下沖:過沖是指超過設定電壓的第一個峰值或谷值。 對于上升沿,指的是最高電壓; 對于下降沿,它指的是最低電壓。 Downrush 是指下一個超過設定電壓的谷值或峰值。 過度的過沖會導致保護二極管工作,導致其過早失效。 過多的下沖會導致錯誤的時鐘或數據錯誤(誤操作)。

振蕩和環繞振蕩:振蕩現象是重復的過沖和下沖。 信號振蕩是由線路上傳輸的電感和電容引起的,屬于欠阻尼狀態,而周圍振蕩屬于過阻尼狀態。 與反射一樣,振蕩和環繞振蕩也是由許多因素引起的。 振蕩可以通過適當的終止來減少,但不能完全消除。

地電平彈跳噪聲和回流噪聲:當電路中有較大的電流浪涌時,會引起地電平彈跳噪聲。 例如,當同時開啟大量芯片輸出時,會在芯片和電路板的電源層流過較大的瞬態電流,芯片封裝和電源層的電感和電阻會導致 電源噪聲,會在真實地平面上產生電壓波動和變化,這種噪聲會影響其他元件的動作。 負載電容的增大、負載電阻的減小、接地電感的增大、開關器件數量的增加都會導致接地彈簧的增大。

傳輸通道電氣特性分析

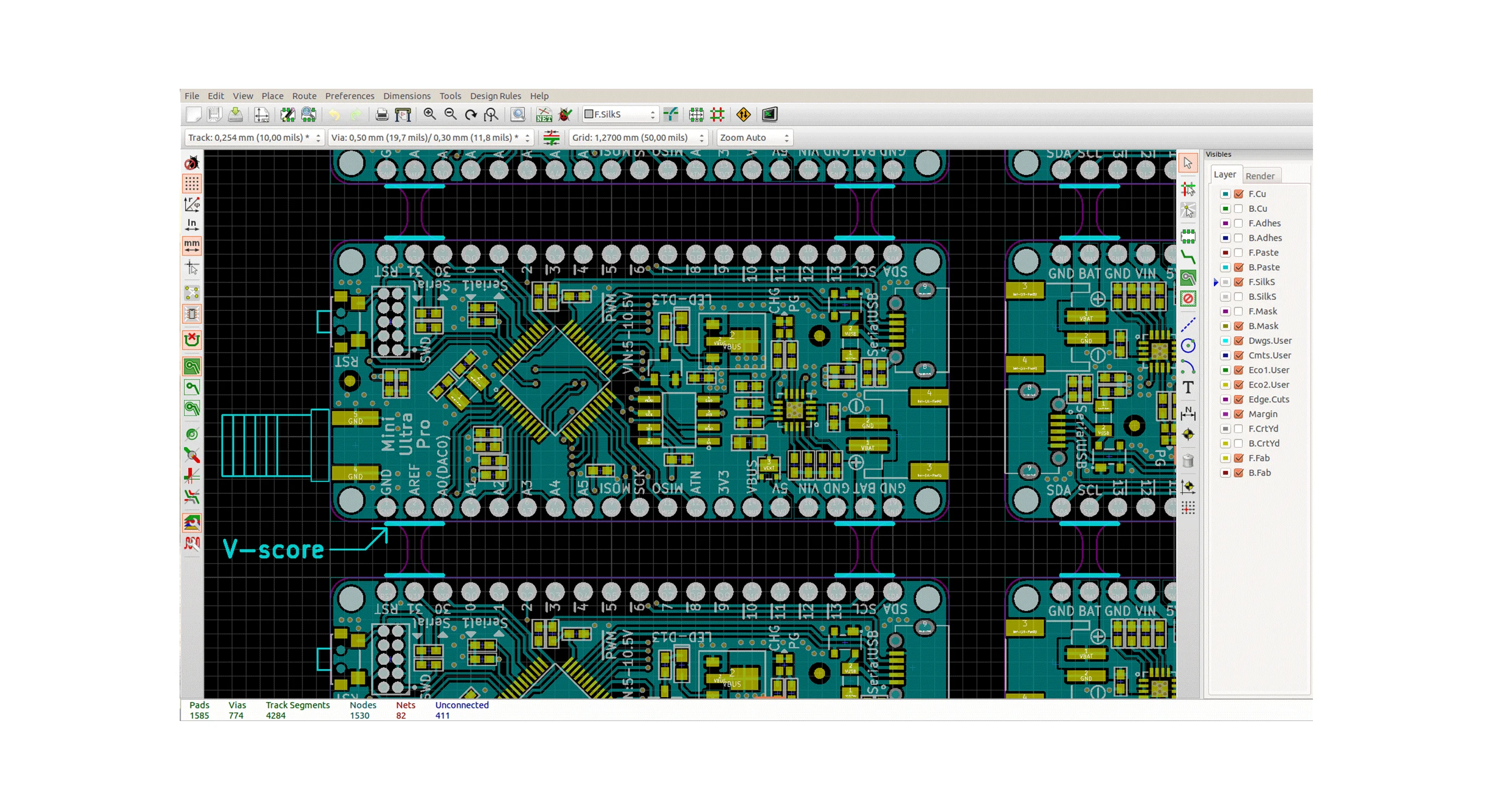

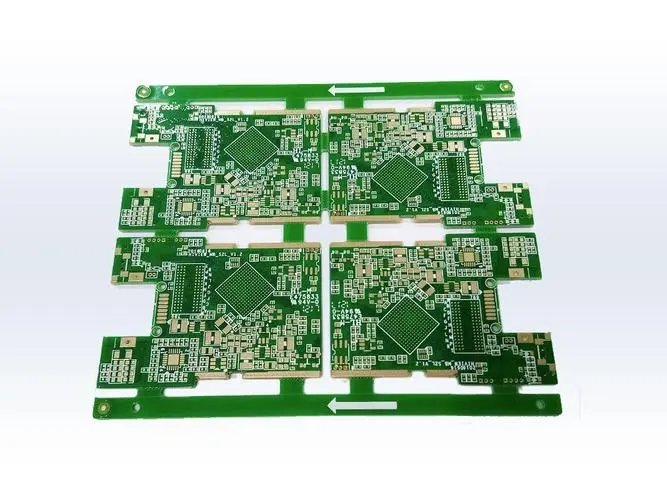

在多層PCB中,大多數傳輸線不僅布置在單層上,而是交錯布置在多層上,各層之間通過過孔連接。 因此,在多層PCB中,典型的傳輸通道主要包括三部分:傳輸線、布線角和過孔。 在低頻情況下,印制線和布線過孔可以看作是連接不同器件管腳的公共電氣連接,不會對信號質量產生太大影響。 但在高頻情況下,印制線、轉角和過孔不僅要考慮它們的連通性,還要考慮它們在高頻下的電氣特性和寄生參數。

高速PCB傳輸線電氣特性分析

在高速PCB的設計中,不可避免地要大量使用不同長度的信號連接線。 與信號本身的變化時間相比,信號通過連接線的延遲時間是不容忽視的。 信號以電磁波的速度在連接線上傳輸。 此時連接線是一個具有電阻、電容和電感的復雜網絡,需要用分布參數系統模型即傳輸線模型來描述。

傳輸線用于將信號從一端傳輸到另一端。 它由兩根一定長度的導線組成,一根稱為信號通路,另一根稱為返回通路。 在低頻電路中,傳輸線的特性表現為純電阻電氣特性。 在高速PCB中,隨著傳輸信號頻率的升高,導體間的容性阻抗減小,而導體上的感性阻抗增大。 信號線將不再只表現出純電阻,即信號不僅在導體上傳輸,而且在導體間的介質中傳輸。 如果信號頻率進一步增加,當j ω L>>R,1/(j ω C) <對于均勻導體,傳輸線的電阻R、寄生電感L和寄生電容C的平均分布(即L1=L2= ...=Ln; C1=C2=...=Cn+1) 不考慮外界環境的變化。 PCB 制造商、PCB 設計人員和 PCBA 制造商將解釋如何提高嵌入式系統中 PCB 信號的完整性。

然后

聯系

電話熱線

13410863085Q Q

微信

- 郵箱